- If it is known that

and

and  , find

, find  and

and  .

.

- If

and

and  , estimate

, estimate  ,

,  and

and  based on the plots below. Re-estimate these currents if

based on the plots below. Re-estimate these currents if  is

increased to

is

increased to  .

.

Note: in the figure above, as the assumed polarities of both

and

and

are the opposite to those assumed in plot (b) below, the negative

signs for both

are the opposite to those assumed in plot (b) below, the negative

signs for both  and

and  in the plot should be dropped.

in the plot should be dropped.

Solution:

![]() ,

,

![]() ,

,

![]() , or

, or

![]() .

.

If ![]() and

and ![]() ,

, ![]() can be estimated from

figure (b), and correspondingly,

can be estimated from

figure (b), and correspondingly, ![]() and

and ![]() . When

. When

![]() ,

, ![]() ,

, ![]() , and

, and ![]() .

.

Solution:

Since the base-emitter pn-junction is forward biased with

Solution: The load line goes through the points

![]() and

and

![]() .

Its intersection with the curve

.

Its intersection with the curve ![]() is approximately at

is approximately at

![]() , where we can also find

, where we can also find

![]() and

and

![]() .

.

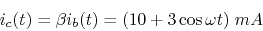

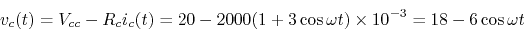

- The base current is

.

Find

.

Find  and

and  as functions of time.

as functions of time.

- Repeat the above for

.

.

- Repeat the above for

.

However, note that the actual base current cannot be negative as

it can only flow from base to emitter but not the other direction,

i.e., all negative parts of

.

However, note that the actual base current cannot be negative as

it can only flow from base to emitter but not the other direction,

i.e., all negative parts of  are zero.

are zero.

Note: As the convention in the schematics of transistor circuits,

the bottom horizontal line is treated as the ground, and all voltages,

such as ![]() ,

, ![]() and

and ![]() are measured with respect to the

ground as the reference point.

are measured with respect to the

ground as the reference point.

Hint: The relationship ![]() is only valid in the

linear region in the middle range of the load line. However, in

the cut-off region (close to the horizontal axis) and the saturation

region (close to the vertical axis), the above relationship no

longer holds and the actual output current

is only valid in the

linear region in the middle range of the load line. However, in

the cut-off region (close to the horizontal axis) and the saturation

region (close to the vertical axis), the above relationship no

longer holds and the actual output current ![]() and

and ![]() can

only be found graphically in the output characteristic plot.

can

only be found graphically in the output characteristic plot.

Solution:

-

-

Clipping happens during the negative half-cycle due to saturation. -

Clipping happens during the positive half-cycle due to cut-off.

Solution: When ![]() ,

, ![]() is cut-off. When

is cut-off. When ![]() ,

,

![]() ,

, ![]() is saturated with

is saturated with ![]() and

and

![]() (instead of

(instead of

![]() ).

The same is true for

).

The same is true for ![]() . From the table below we see that the

circuit is a NOR (not OR) gate (high voltage for True and low

voltage for False).

. From the table below we see that the

circuit is a NOR (not OR) gate (high voltage for True and low

voltage for False).