# Lecture 4: Nonideal Transistor Theory

NEIL H. E. WESTE DAVID MONEY HARRIS

### Outline

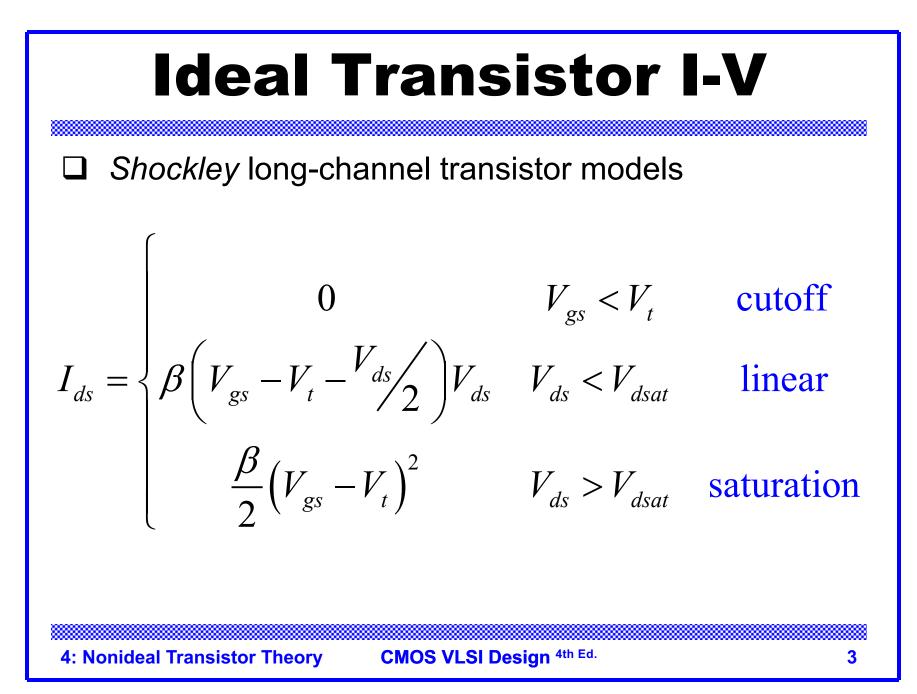

Nonideal Transistor Behavior

- High Field Effects

- Mobility Degradation

- Velocity Saturation

- Channel Length Modulation

- Threshold Voltage Effects

- Body Effect

- Drain-Induced Barrier Lowering

- Short Channel Effect

- Leakage

- Subthreshold Leakage

- Gate Leakage

- Junction Leakage

Process and Environmental Variations

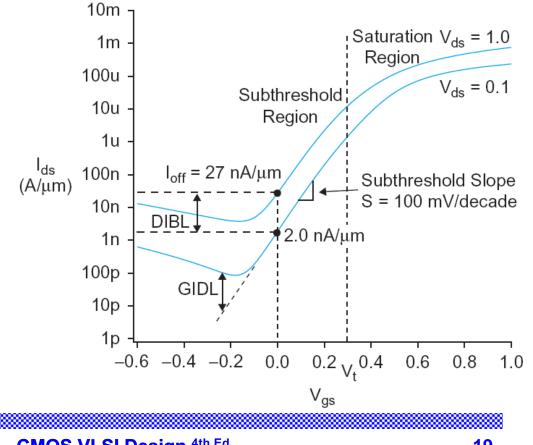

#### **ON and OFF Current**

$$\Box I_{on} = I_{ds} @ V_{gs} = V_{ds} = V_{DD}$$

- Saturation

$$\Box \quad \mathbf{I}_{off} = \mathbf{I}_{ds} @ \mathbf{V}_{gs} = 0, \ \mathbf{V}_{ds} = \mathbf{V}_{DD}$$

$$- Cutoff$$

**4: Nonideal Transistor Theory**

CMOS VLSI Design <sup>4th Ed.</sup>

#### **Electric Fields Effects**

- □ Vertical electric field:  $E_{vert} =$

- Attracts carriers into channel

- Long channel:  $Q_{channel}$  proportional to  $E_{vert}$

- □ Lateral electric field:  $E_{lat} =$

- Accelerates carriers from drain to source

- Long channel: v =  $\mu E_{lat}$

### **Coffee Cart Analogy**

- Tired student runs from VLSI lab to coffee cart

- □ Freshmen are pouring out of the physics lecture hall

- $\Box$  V<sub>ds</sub> is how long you have been up

- Your velocity = fatigue × mobility

- $\Box$  V<sub>gs</sub> is a wind blowing you against the glass (SiO<sub>2</sub>) wall

- $\hfill \Box$  At high  $V_{gs},$  you are buffeted against the wall

- Mobility degradation

- $\hfill \hfill \hfill$

- Velocity saturation

- Don't confuse this with the saturation region

#### **Mobility Degradation**

High E<sub>vert</sub> effectively reduces mobility

Collisions with oxide interface

CMOS VLSI Design <sup>4th Ed.</sup>

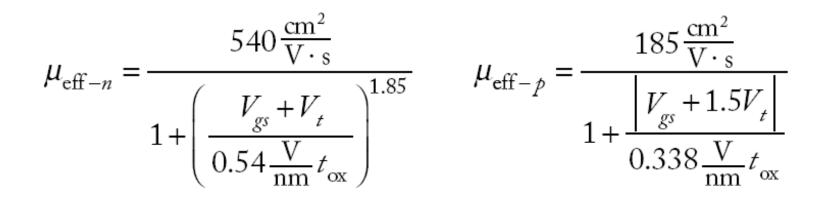

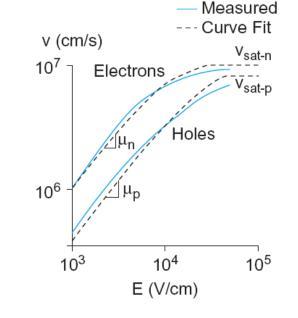

# **Velocity Saturation**

□ At high E<sub>lat</sub>, carrier velocity rolls off

- Carriers scatter off atoms in silicon lattice

- Velocity reaches  $v_{sat}$

- Electrons: 10<sup>7</sup> cm/s

- Holes: 8 x 10<sup>6</sup> cm/s

$E < E_c$   $E_c$

$E \ge E_c$

Better model

$\frac{\mu_{\rm eff}E}{1+\frac{E}{E_c}}$

4: Nonideal Transistor Theory

CMOS VLSI Design 4th Ed.

# **Vel Sat I-V Effects**

$\hfill\square$  Ideal transistor ON current increases with  $V_{DD}{}^2$

$$I_{ds} = \mu C_{ox} \frac{W}{L} \frac{\left(V_{gs} - V_{t}\right)^{2}}{2} = \frac{\beta}{2} \left(V_{gs} - V_{t}\right)^{2}$$

□ Velocity-saturated ON current increases with V<sub>DD</sub>

$$I_{ds} = C_{ox}W(V_{gs} - V_t)v_{sat}$$

Real transistors are partially velocity saturated

- Approximate with  $\alpha$ -power law model

- $I_{ds}$  scales with  $V_{DD}{}^{\alpha}$

- $-1 < \alpha < 2$  determined empirically ( $\approx 1.3$  for 65 nm)

#### $\alpha$ -Power Model

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_t & \text{cutoff} \\ I_{dsat} \frac{V_{ds}}{V_{dsat}} & V_{ds} < V_{dsat} & \text{linear} \\ I_{dsat} & V_{ds} > V_{dsat} & \text{saturation} \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\$$

$$I_{dsat} = P_c \frac{\beta}{2} \left( V_{gs} - V_t \right)^{\alpha}$$

$$V_{dsat} = P_v \left( V_{gs} - V_t \right)^{\alpha/2}$$

4: Nonideal Transistor Theory

CMOS VLSI Design <sup>4th Ed.</sup>

\_ V<sub>ds</sub>

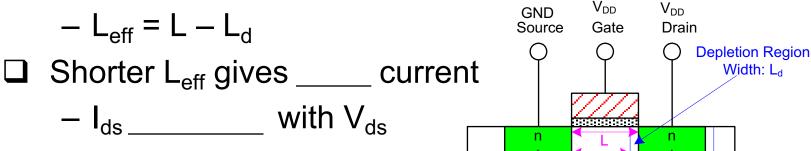

# **Channel Length Modulation**

□ Reverse-biased p-n junctions form a *depletion region*

- Region between n and p with no carriers

- Width of depletion  $L_d$  region grows with reverse bias

CMOS VLSI Design 4th Ed.

Even in saturation

**4: Nonideal Transistor Theory**

12

<sup>p</sup> GND

bulk Si

# **Chan Length Mod I-V**

$$I_{ds} = \frac{\beta}{2} \left( V_{gs} - V_t \right)^2 \left( 1 + \lambda V_{ds} \right)$$

- $\Box$   $\lambda$  = channel length modulation coefficient

- not feature size

- Empirically fit to I-V characteristics

### **Threshold Voltage Effects**

- $\Box$  V<sub>t</sub> is V<sub>gs</sub> for which the channel starts to invert

- Ideal models assumed V<sub>t</sub> is constant

- Really depends (weakly) on almost everything else:

- Body voltage: Body Effect

- Drain voltage: Drain-Induced Barrier Lowering

- Channel length: Short Channel Effect

# **Body Effect**

- Body is a fourth transistor terminal

- V<sub>sb</sub> affects the charge required to invert the channel

- Increasing  $V_s$  or decreasing  $V_b$  increases  $V_t$

$$V_t = V_{t0} + \gamma \left( \sqrt{\phi_s + V_{sb}} - \sqrt{\phi_s} \right)$$

- $\Box$  V<sub>t0</sub> = nominal threshold voltage

- $\Box \quad \phi_{s} = surface \ potential \ at \ threshold$  $\phi_{s} = 2v_{T} \ln \frac{N_{A}}{n_{i}}$

- Depends on doping level N<sub>A</sub>

- And intrinsic carrier concentration n<sub>i</sub>

- γ = body effect coefficient

$$\gamma = \frac{t_{\rm ox}}{\varepsilon_{\rm ox}} \sqrt{2q\varepsilon_{\rm si}N_A} = \frac{\sqrt{2q\varepsilon_{\rm si}N_A}}{C_{\rm ox}}$$

### **Body Effect Cont.**

□ For small source-to-body voltage, treat as linear

$$V_t = V_{t0} + k_\gamma V_{sb}$$

$$k_{\gamma} = \frac{\gamma}{2\sqrt{\phi_s}} = \frac{\sqrt{\frac{q\varepsilon_{si}N_A}{\upsilon_T \ln \frac{N_A}{n_i}}}}{2C_{ox}}$$

## DIBL

- Electric field from drain affects channel

- More pronounced in small transistors where the drain is closer to the channel

- Drain-Induced Barrier Lowering

- Drain voltage also affect V<sub>t</sub>

$$V_t' = V_t - \eta V_{ds}$$

High drain voltage causes current to

### **Short Channel Effect**

- In small transistors, source/drain depletion regions extend into the channel

- Impacts the amount of charge required to invert the channel

- And thus makes V<sub>t</sub> a function of channel length

- $\Box$  Short channel effect: V<sub>t</sub> increases with L

- Some processes exhibit a reverse short channel effect in which  $V_t$  decreases with L

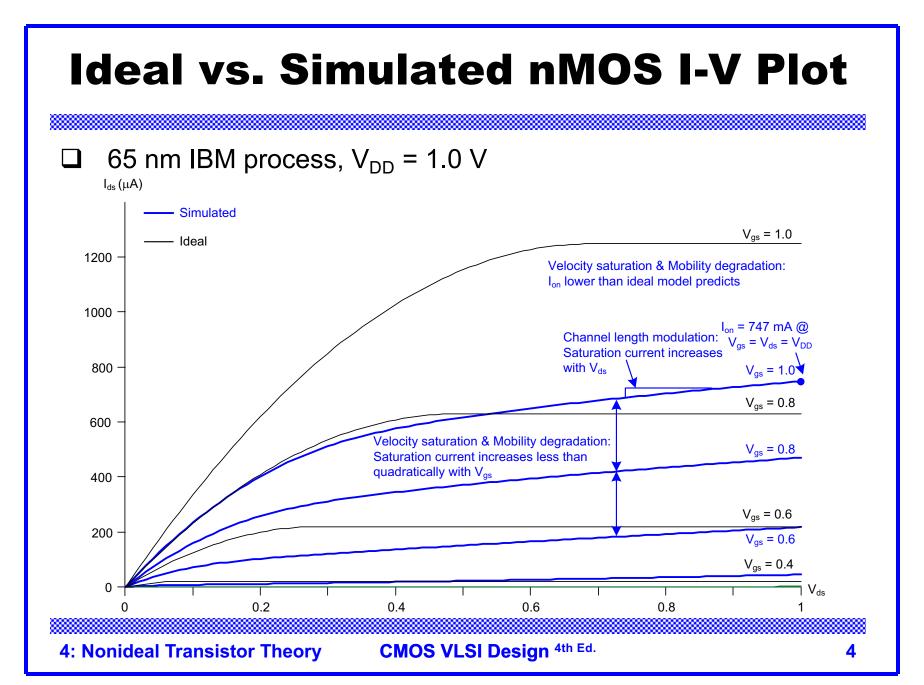

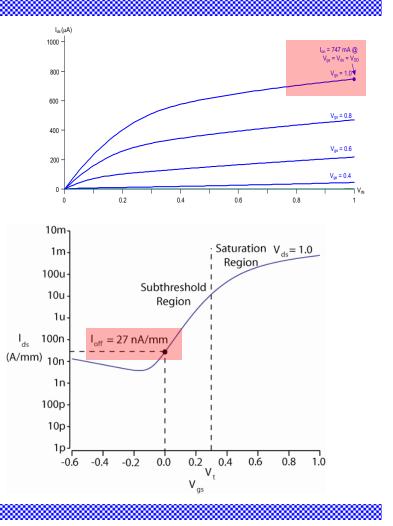

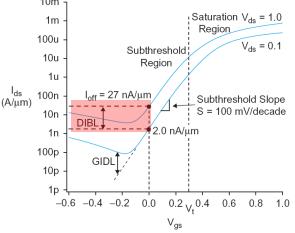

#### Leakage

- What about current in cutoff?

- Simulated results

- What differs?

CMOS VLSI Design 4th Ed.

## Leakage Sources

- Subthreshold conduction

- Transistors can't abruptly turn ON or OFF

- Dominant source in contemporary transistors

- Gate leakage

- Tunneling through ultrathin gate dielectric

- Junction leakage

- Reverse-biased PN junction diode current

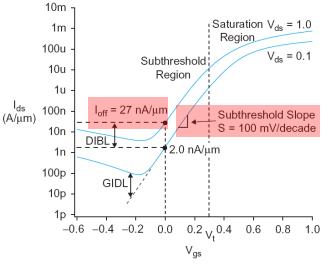

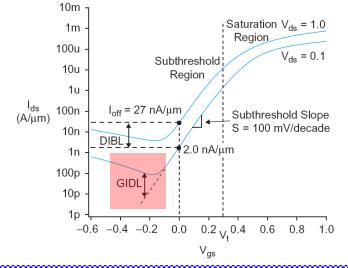

# **Subthreshold Leakage**

Subthreshold leakage exponential with V<sub>gs</sub>

$$I_{ds} = I_{ds0} e^{\frac{V_{gs} - V_{t0} + \eta V_{ds} - k_{\gamma} V_{sb}}{n v_T}} \left( 1 - e^{\frac{-V_{ds}}{v_T}} \right)$$

- **n** is process dependent

- typically 1.3-1.7

❑ Rewrite relative to I<sub>off</sub> on log scale

$$I_{ds} = I_{\text{off}} 10^{\frac{V_{gs} + \eta (V_{ds} - V_{dd}) - k\gamma V_{sb}}{S}} \left(1 - e^{\frac{-V_{ds}}{v_t}}\right) \qquad S = \left[\frac{d \left(\log_{10} I_{ds}\right)}{dV_{gs}}\right]^{-1} = nv_T \ln 10$$

I S ≈ 100 mV/decade @ room temperature

4: Nonideal Transistor Theory CMOS VLSI Design <sup>4th Ed.</sup>

### **Gate Leakage**

10<sup>9</sup>

10<sup>6</sup>

10<sup>3</sup>

100

10-3

10-6

$10^{-9}$

0

$J_{\rm G}$  (A/cm<sup>2</sup>)

V<sub>DD</sub> trend

0.3

0.6

0.9

$V_{DD}$

1.2

1.5

From [Song01]

1.8

- Carriers tunnel thorough very thin gate oxides

- Exponentially sensitive to t<sub>ox</sub> and V<sub>DD</sub>

$$I_{\text{gate}} = W\!A \left(\frac{V_{DD}}{t_{\text{ox}}}\right)^2 e^{-B \frac{t_{\text{ox}}}{V_{DD}}}$$

- A and B are tech constants

- Greater for electrons

- So nMOS gates leak more

- Negligible for older processes ( $t_{ox} > 20 \text{ Å}$ )

- **I** Critically important at 65 nm and below ( $t_{ox} \approx 10.5 \text{ Å}$ )

10 Å

12 Å

15 Å 19 Å

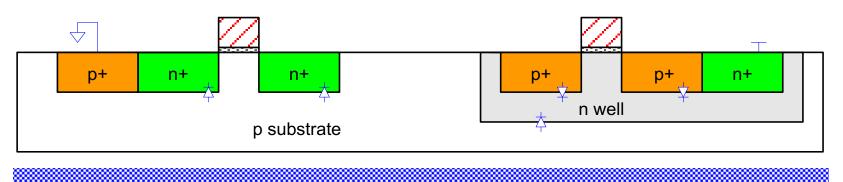

# **Junction Leakage**

□ Reverse-biased p-n junctions have some leakage

- Ordinary diode leakage

- Band-to-band tunneling (BTBT)

- Gate-induced drain leakage (GIDL)

CMOS VLSI Design <sup>4th Ed.</sup>

# **Diode Leakage**

□ Reverse-biased p-n junctions have some leakage

$$I_D = I_S \left( e^{\frac{V_D}{v_T}} - 1 \right)$$

□ At any significant negative diode voltage,  $I_D = -I_s$

I<sub>s</sub> depends on doping levels

- And area and perimeter of diffusion regions

- Typically < 1 fA/ $\mu$ m<sup>2</sup> (negligible)

#### **Band-to-Band Tunneling**

□ Tunneling across heavily doped p-n junctions

- Especially sidewall between drain & channel when *halo doping* is used to increase V<sub>t</sub>

- Increases junction leakage to significant levels

$$I_{BTBT} = WX_j A \frac{E_j}{E_g^{0.5}} V_{dd} e^{-B \frac{E_g^{1.5}}{E_j}} \qquad \qquad E_j = \sqrt{\frac{2qN_{balo}N_{sd}}{\varepsilon \left(N_{balo} + N_{sd}\right)}} \left(V_{DD} + v_T \ln \frac{N_{balo}N_{sd}}{n_i^2}\right)$$

- X<sub>j</sub>: sidewall junction depth

- E<sub>g</sub>: bandgap voltage

- A, B: tech constants

#### **Gate-Induced Drain Leakage**

Occurs at overlap between gate and drain

- Most pronounced when drain is at  $V_{\text{DD}},$  gate is at a negative voltage

- Thwarts efforts to reduce subthreshold leakage using a negative gate voltage

### So What?

- □ So what if transistors are not ideal?

- They still behave like switches.

- □ But these effects matter for...

- Supply voltage choice

- Logical effort

- Quiescent power consumption

- Pass transistors

- Temperature of operation

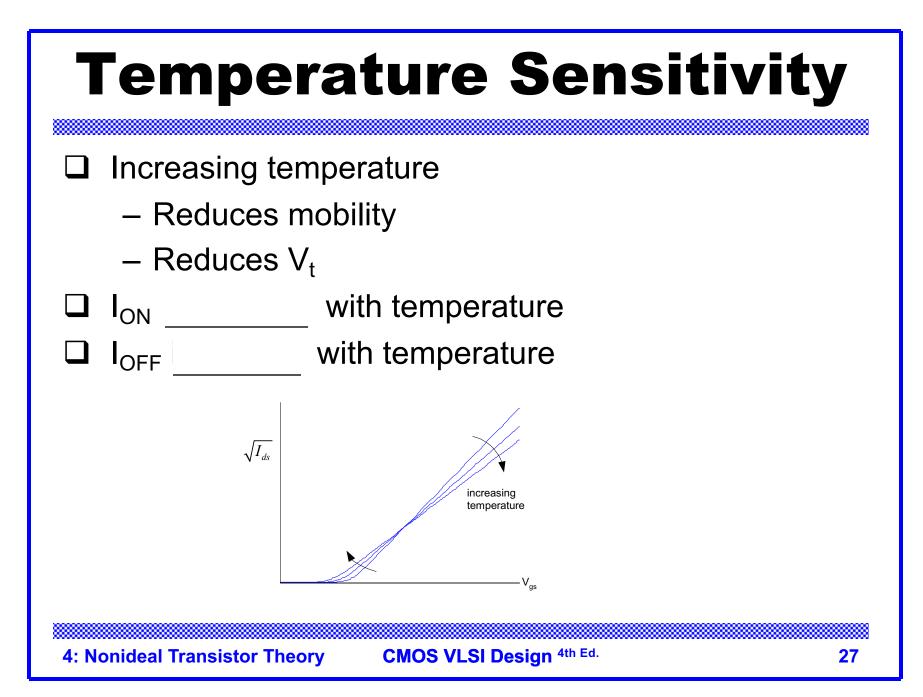

### **Environmental Variation**

$\hfill\square\hfill V_{DD}$  and T also vary in time and space

General Fast:

| Corner | Voltage | Temperature |  |

|--------|---------|-------------|--|

| F      |         |             |  |

| Т      | 1.8     | 70 C        |  |

| S      |         |             |  |

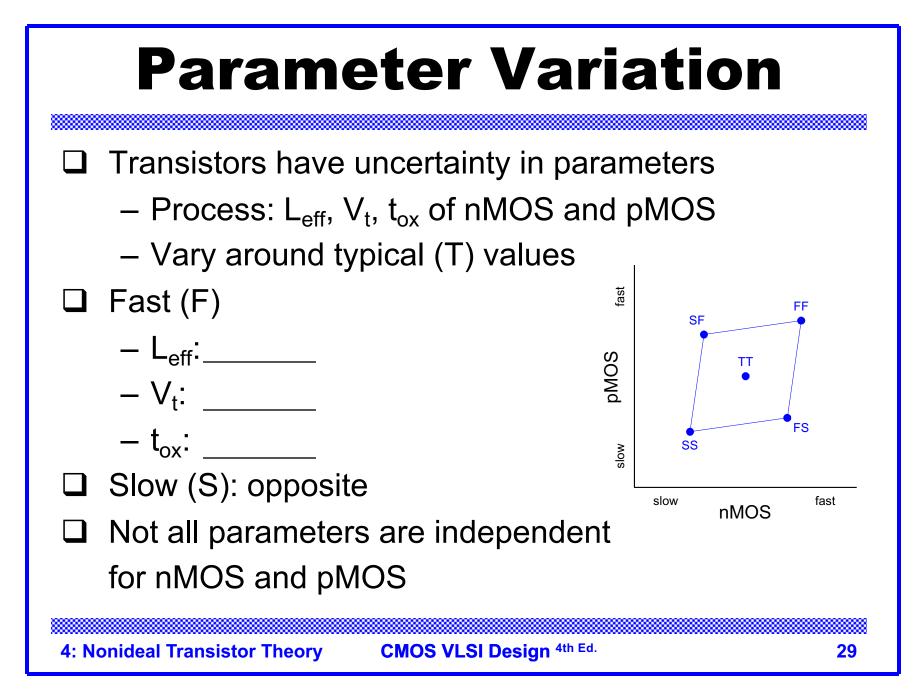

#### **Process Corners**

- Process corners describe worst case variations

- If a design works in all corners, it will probably work for any variation.

- Describe corner with four letters (T, F, S)

- nMOS speed

- pMOS speed

- Voltage

- Temperature

### **Important Corners**

□ Some critical simulation corners include

| Purpose      | nMOS | pMOS | V <sub>DD</sub> | Тетр |

|--------------|------|------|-----------------|------|

| Cycle time   |      |      |                 |      |

| Power        |      |      |                 |      |

| Subthreshold |      |      |                 |      |

| leakage      |      |      |                 |      |