# Lecture 16: CAMs, ROMs, PLAs

NEIL H. E. WESTE DAVID MONEY HARRIS

# Outline

- Content-Addressable Memories

- Read-Only Memories

- Programmable Logic Arrays

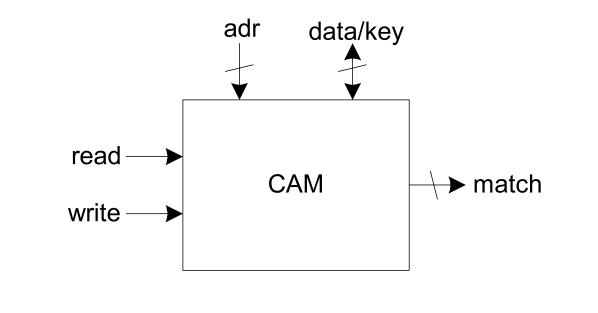

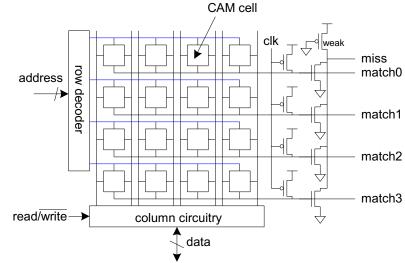

# CAMs

- □ Extension of ordinary memory (e.g. SRAM)

- Read and write memory as usual

- Also match to see which words contain a key

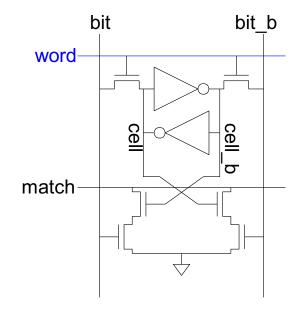

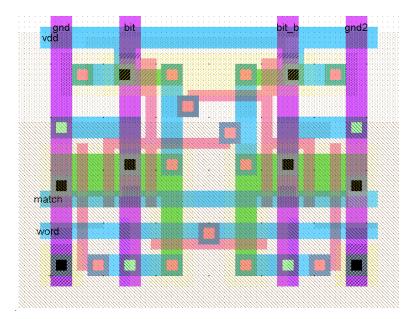

# **10T CAM Cell**

# Add four match transistors to 6T SRAM - 56 x 43 λ unit cell

20: CAMs, ROMs, and PLAs

# **CAM Cell Operation**

- Read and write like ordinary SRAM

- For matching:

- Leave wordline low

- Precharge matchlines

- Place key on bitlines

- Matchlines evaluate

- Miss line

- Pseudo-nMOS NOR of match lines

- Goes high if no words match

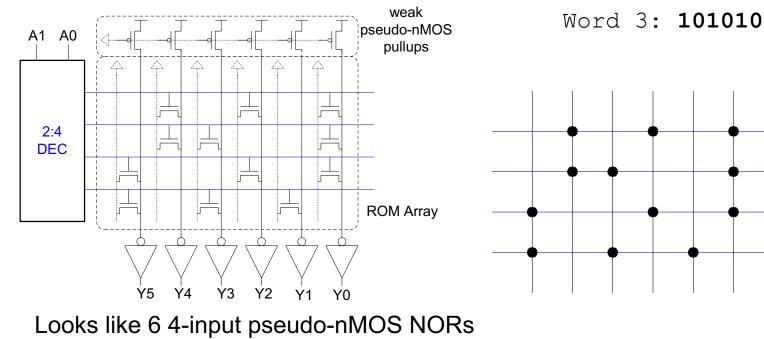

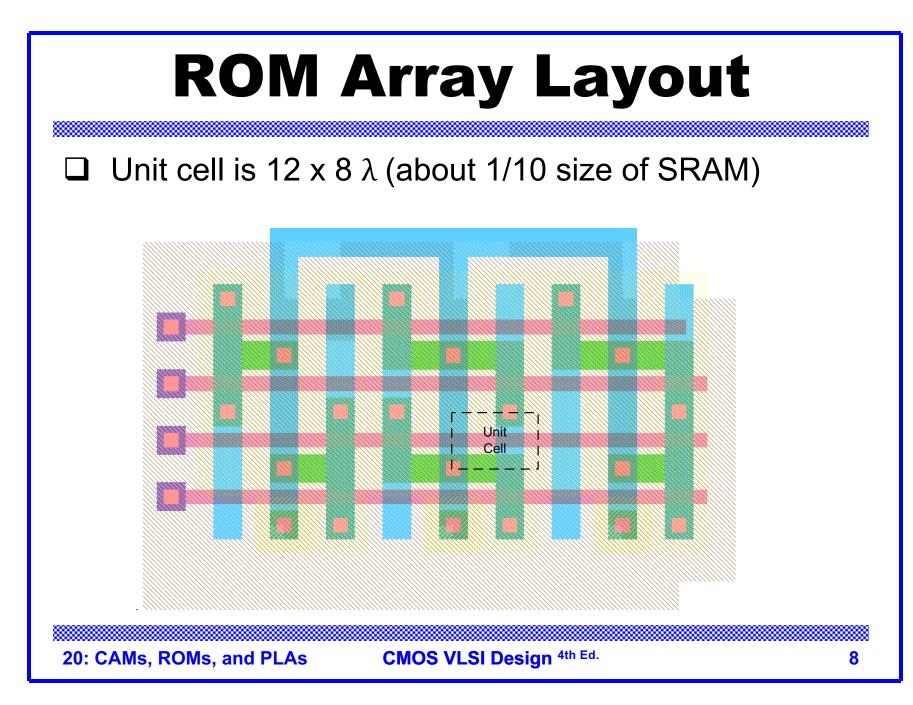

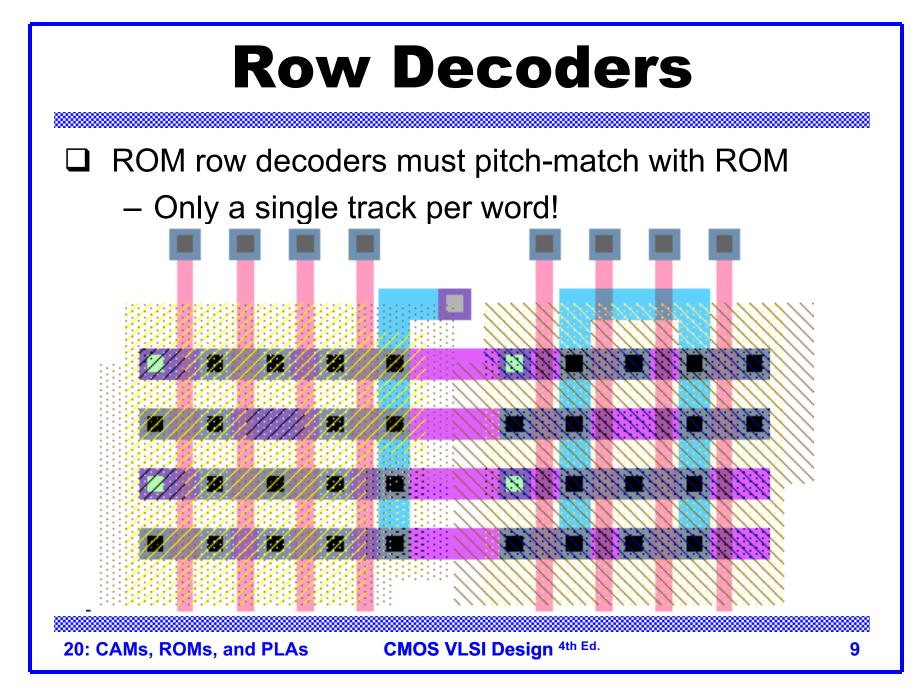

# **Read-Only Memories**

- Read-Only Memories are nonvolatile

- Retain their contents when power is removed

- Mask-programmed ROMs use one transistor per bit

- Presence or absence determines 1 or 0

# **ROM Example**

#### □ 4-word x 6-bit ROM

- Represented with dot diagram

- Dots indicate 1's in ROM

20: CAMs, ROMs, and PLAs CMOS VLSI Design <sup>4th Ed.</sup>

Word 0: 010101

Word 1: 011001

Word 2: 100101

# **PROMs and EPROMs**

- Programmable ROMs

- Build array with transistors at every site

- Burn out fuses to disable unwanted transistors

- Electrically Programmable ROMs

- Use floating gate to turn off unwanted transistors

- EPROM, EEPROM, Flash

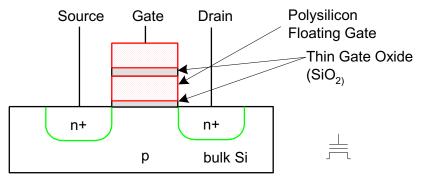

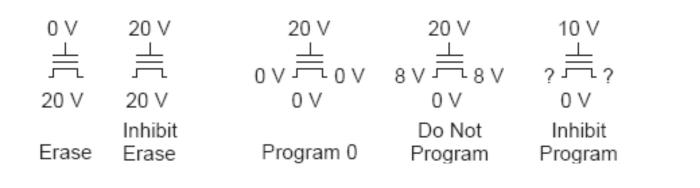

# **Flash Programming**

- □ Charge on floating gate determines V<sub>t</sub>

- $\Box \quad \text{Logic 1: negative } V_t$

- $\Box \quad \text{Logic 0: positive } V_t$

- Cells erased to 1 by applying a high body voltage so that electrons tunnel off floating gate into substrate

- Programmed to 0 by applying high gate voltage

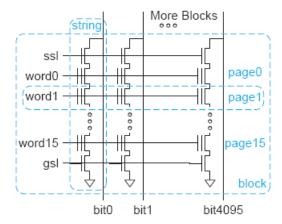

### **NAND Flash**

- High density, low cost / bit

- Programmed one page at a time

- Erased one block at a time

- Example:

- 4096-bit pages

- 16 pages / 8 KB block

- Many blocks / memory

### 64 Gb NAND Flash

- □ 64K cells / page

- $\Box 4 \text{ bits / cell (multiple V}_t)$

- 64 cells / string

- 256 pages / block

- 2K blocks / plane

- □ 2 planes

[Trinh09]

20: CAMs, ROMs, and PLAs

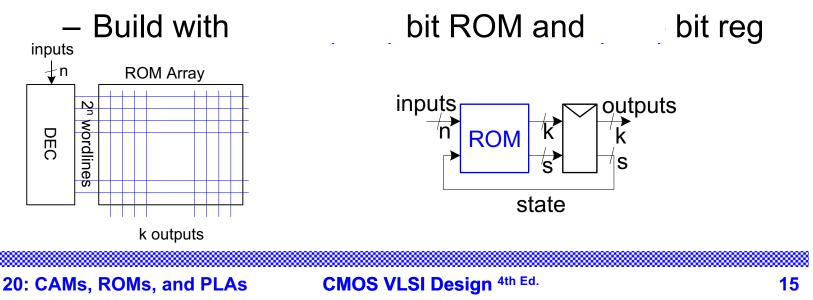

# **Building Logic with ROMs**

□ Use ROM as lookup table containing truth table

- n inputs, k outputs requires words x bits

- Changing function is easy reprogram ROM

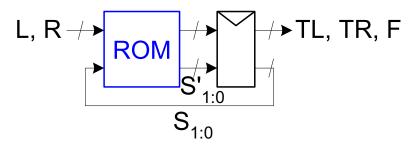

- □ Finite State Machine

- n inputs, k outputs, s bits of state

# **Example: RoboAnt**

#### Let's build an Ant

Sensors: Antennae (L,R) – 1 when in contact Actuators: Legs Forward step F Ten degree turns TL, TR

Goal: make our ant smart enough to get out of a maze

Strategy: keep right antenna on wall

(RoboAnt adapted from MIT 6.004 2002 OpenCourseWare by Ward and Terman)

20: CAMs, ROMs, and PLAs

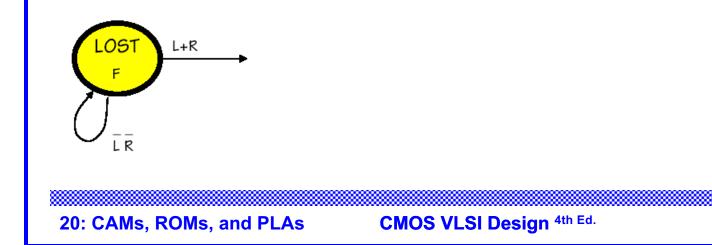

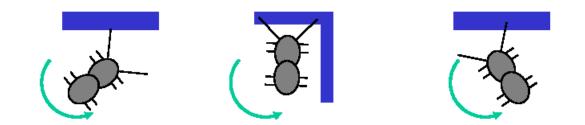

### Lost in space

# Action: go forward until we hit something Initial state

### Bonk!!!

□ Action: turn left (rotate counterclockwise)

- Until we don't touch anymore

# A little to the right

- □ Action: step forward and turn right a little

- Looking for wall

20: CAMs, ROMs, and PLAs CMOS VLSI Design <sup>4th Ed.</sup>

# Then a little to the left

Action: step and turn left a little, until not touching

20

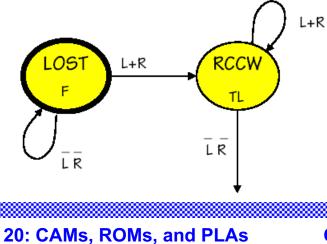

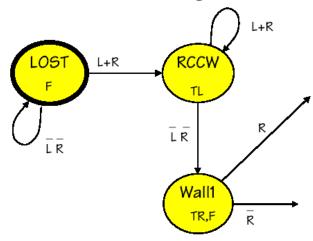

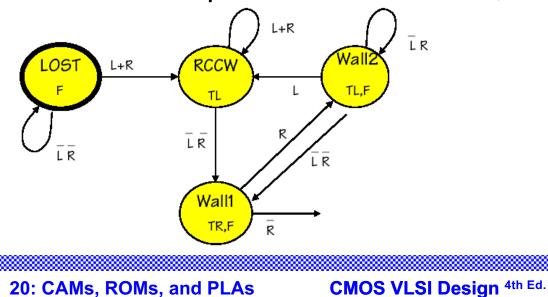

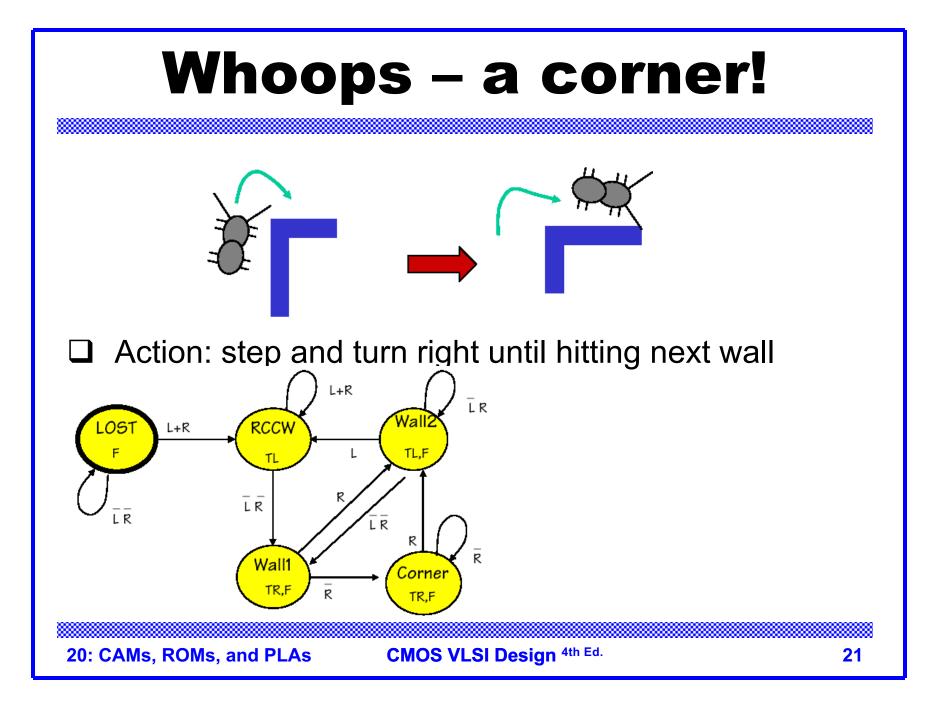

#### Simplification Merge equivalent states where possible L+R L+R ĪR ĪR Wall Wall RCCW RCCW -05 L+R \_OST L+R TL,F TL,F TL TL LR LR LR LR ĪR ĹŔ R Wall1 Wall1 Corner TR,F TR,F R TR,F R CMOS VLSI Design <sup>4th Ed.</sup> 22 20: CAMs, ROMs, and PLAs

# **State Transition Table**

|              | S <sub>1:0</sub> | L | R | S <sub>1:0</sub> ' | TR | TL | F |

|--------------|------------------|---|---|--------------------|----|----|---|

| /            | 00               | 0 | 0 | 00                 | 0  | 0  | 1 |

| Lost         | 00               | 1 | Х | 01                 | 0  | 0  | 1 |

|              | 00               | 0 | 1 | 01                 | 0  | 0  | 1 |

| /            | 01               | 1 | Х | 01                 | 0  | 1  | 0 |

| RCCW 🔇       | 01               | 0 | 1 | 01                 | 0  | 1  | 0 |

| $\backslash$ | 01               | 0 | 0 | 10                 | 0  | 1  | 0 |

| Wall1 🤇      | 10               | Х | 0 | 10                 | 1  | 0  | 1 |

|              | 10               | Х | 1 | 11                 | 1  | 0  | 1 |

| /            | 11               | 1 | Х | 01                 | 0  | 1  | 1 |

| Wall2 🔇      | 11               | 0 | 0 | 10                 | 0  | 1  | 1 |

| $\backslash$ | 11               | 0 | 1 | 11                 | 0  | 1  | 1 |

20: CAMs, ROMs, and PLAs

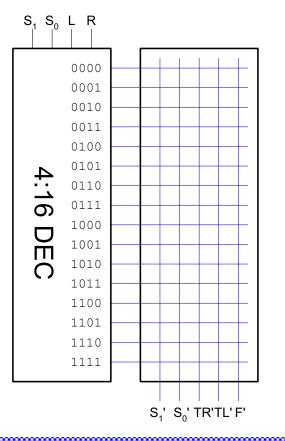

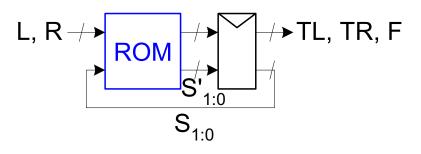

# **ROM Implementation**

#### □ 16-word x 5 bit ROM

20: CAMs, ROMs, and PLAs

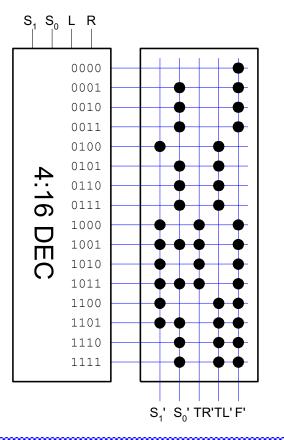

# **ROM Implementation**

□ 16-word x 5 bit ROM

20: CAMs, ROMs, and PLAs

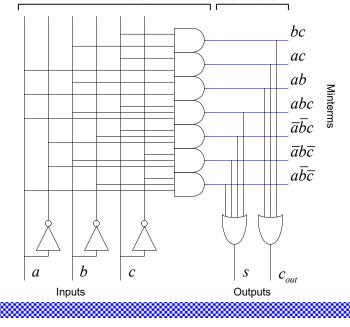

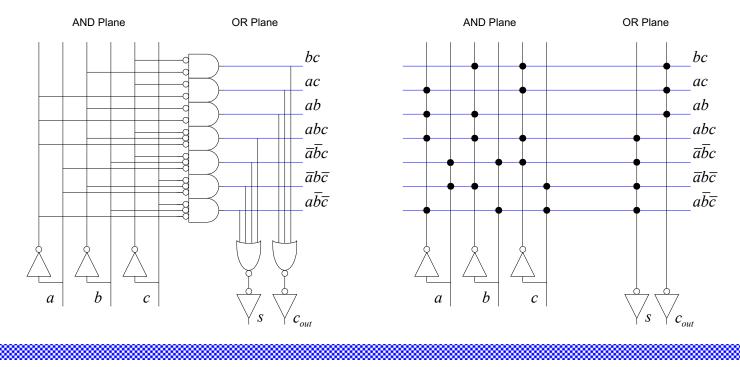

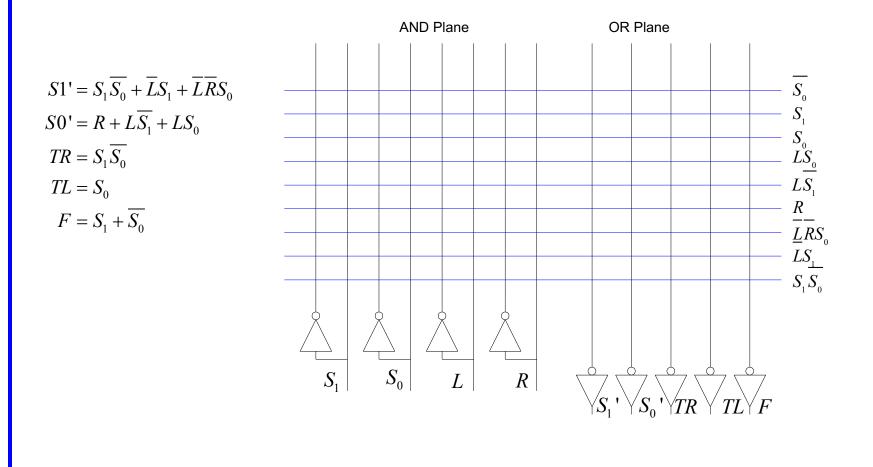

# PLAs

- A Programmable Logic Array performs any function in sum-of-products form.

- Literals: inputs & complements

- Products / Minterms: AND of literals

AND Plane

- Outputs: OR of Minterms

- Example: Full Adder

$$s = a\overline{b}\overline{c} + \overline{a}b\overline{c} + \overline{a}\overline{b}c + abc$$

$$c_{\text{out}} = ab + bc + ac$$

**OR** Plane

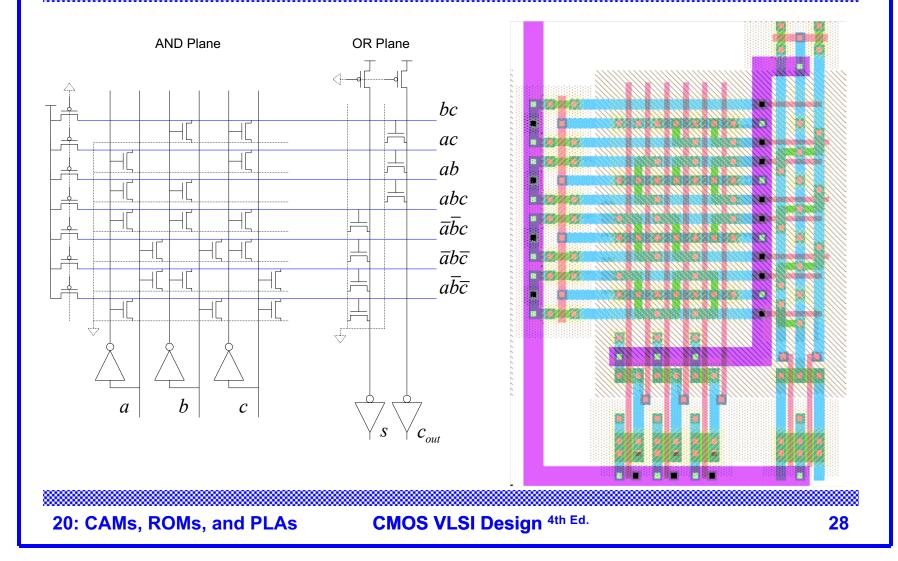

# **NOR-NOR PLAs**

ANDs and ORs are not very efficient in CMOS

Dynamic or Pseudo-nMOS NORs are very efficient

Use DeMorgan's Law to convert to all NORs

20: CAMs, ROMs, and PLAs

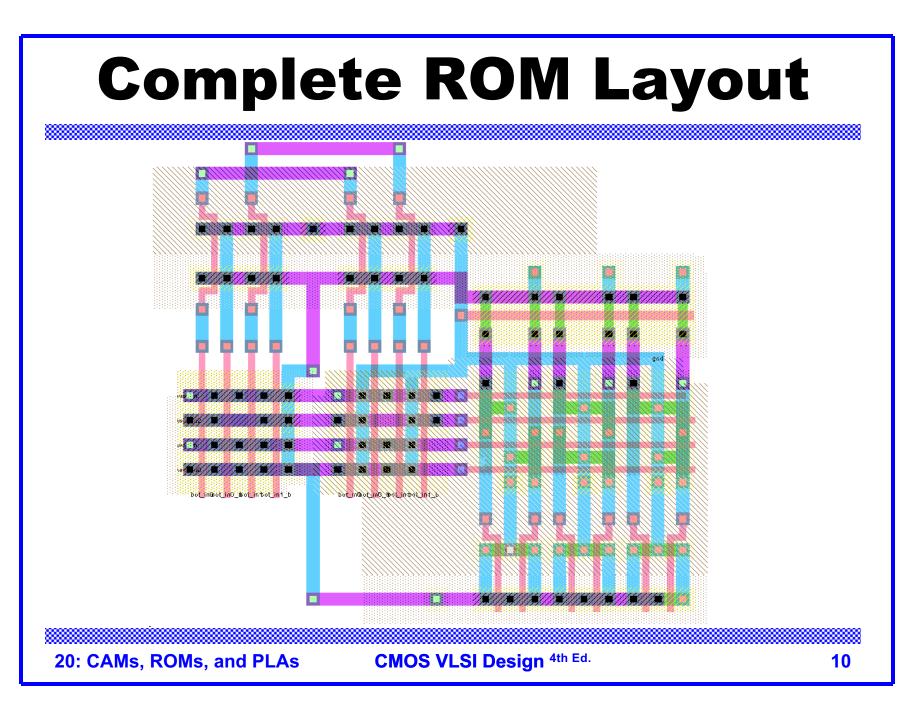

# **PLA Schematic & Layout**

# PLAs vs. ROMs

- The OR plane of the PLA is like the ROM array

- The AND plane of the PLA is like the ROM decoder

- PLAs are more flexible than ROMs

- No need to have 2<sup>n</sup> rows for n inputs

- Only generate the minterms that are needed

- Take advantage of logic simplification

# **Example: RoboAnt PLA**

Convert state transition table to logic equations

| S <sub>1:0</sub> | L | R | S <sub>1:0</sub> ' | TR | TL | F | <b>S1' S</b> <sub>1</sub> <b>S</b> <sub>0</sub>                             |

|------------------|---|---|--------------------|----|----|---|-----------------------------------------------------------------------------|

| 00               | 0 | 0 | 00                 | 0  | 0  | 1 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                        |

| 00               | 1 | X | 01                 | 0  | 0  | 1 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                        |

| 00               | 0 | 1 | 01                 | 0  | 0  | 1 |                                                                             |

| 01               | 1 | X | 01                 | 0  | 1  | 0 | $S_1' = S_1 \overline{S_0} + \overline{L}S_1 + \overline{L}\overline{R}S_0$ |

| 01               | 0 | 1 | 01                 | 0  | 1  | 0 | so' s <sub>1</sub> s <sub>0</sub>                                           |

| 01               | 0 | 0 | 10                 | 0  | 1  | 0 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                        |

| 10               | X | 0 | 10                 | 1  | 0  | 1 |                                                                             |

| 10               | Х | 1 | 11                 | 1  | 0  | 1 | 10 1 1 0                                                                    |

| 11               | 1 | X | 01                 | 0  | 1  | 1 | $S_0' = R + LS_1 + LS_0$ $TP - S\overline{S}$                               |

| 11               | 0 | 0 | 10                 | 0  | 1  | 1 | $TR = S_1 S_0$ $TL = S_0$                                                   |

| 11               | 0 | 1 | 11                 | 0  | 1  | 1 | $F = S_1 + \overline{S_0}$                                                  |

20: CAMs, ROMs, and PLAs

# **RoboAnt Dot Diagram**

20: CAMs, ROMs, and PLAs