# **Direct Memory Access**

Lecture 21

Josh Brake

Harvey Mudd College

### **Learning Objectives**

By the end of this lecture you will be able to:

- Explain what direct memory access is used for and how it works

- Configure DMA on our MCU

### Outline

- What is Direct Memory Access?

- How does DMA work on the MCU?

- Activity

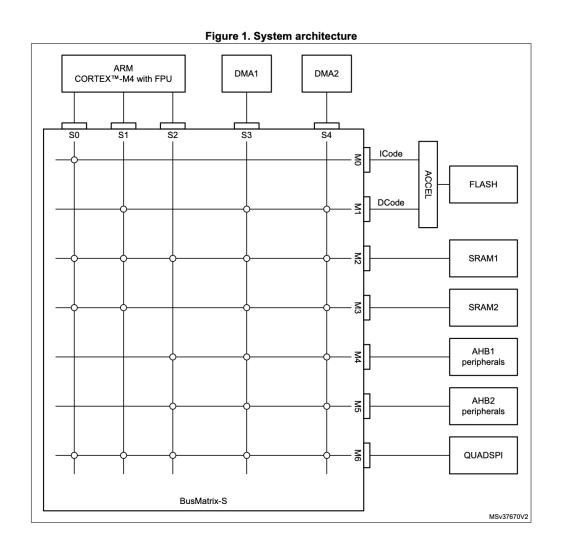

## Recall STM32L432KC System Architecture

#### **Direct Memory Access**

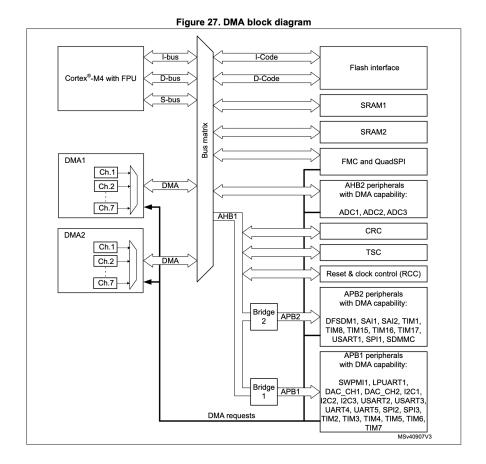

- Used to provide high-speed data transfer between peripherals and memory without CPU action

- DMA controller connects to the AHB bus

- The MCU has two DMA controllers with 7 channels each (total of 14 channels)

- Each channel has a mux which enables various DMA request sources to be selected

### **DMA Block Diagram**

#### 4 modes

- Peripheral-to-memory

- Peripheral-to-peripheral

- Memory-to-peripheral

- Memory-to-memory

RM 0394 p. 300

#### **Activity**

The goal of this example project is to use the direct memory access (DMA) controller on the MCU to enable automatic printing of data to the computer terminal via UART without the need for processor intervention. We will be designing a system to meet the following requirements.

#### **Specifications**

- 1. Print out a single character from a specified character array at a frequency of ~10 Hz (one character every 100 milliseconds).

- 2. Use a UART baud rate of 9600.

- 3. Use update events from Timer 2 (TIM2) to trigger the DMA requests.

- 4. Use DMA Controller 1 (DMA1) to handle the direct memory transfers from the character array to the UART peripheral.

### **Activity Steps and Hints**

- Work through worksheet.

- After completing worksheet, create a new project and import demo source code.

#### **DMA Channel Selection**

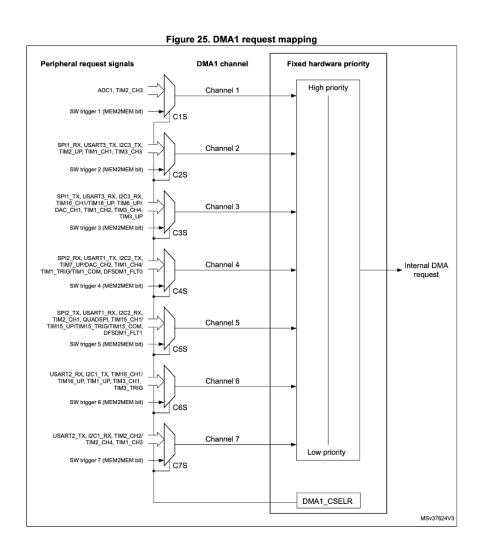

### **DMA1** Request Mapping Table

Table 41. DMA1 requests for each channel

| CxS[3:0] | Channel 1 | Channel 2           | Channel 3 | Channel 4              | Channel 5                      | Channel 6                      | Channel 7             |

|----------|-----------|---------------------|-----------|------------------------|--------------------------------|--------------------------------|-----------------------|

| 0000     | ADC1      | ADC2 <sup>(1)</sup> | -         | -                      | DFSDM1_<br>FLT0 <sup>(2)</sup> | DFSDM1_<br>FLT1 <sup>(2)</sup> | -                     |

| 0001     | -         | SPI1_RX             | SPI1_TX   | SPI2_RX <sup>(3)</sup> | SPI2_TX <sup>(3)</sup>         | SAI2_A <sup>(4)</sup>          | SAI2_B <sup>(4)</sup> |

Table 41. DMA1 requests for each channel (continued)

| CxS[3:0] | Channel 1 | Channel 2               | Channel 3                                         | Channel 4                          | Channel 5                                        | Channel 6                            | Channel 7            |

|----------|-----------|-------------------------|---------------------------------------------------|------------------------------------|--------------------------------------------------|--------------------------------------|----------------------|

| 0010     | -         | USART3_TX               | USART3_RX                                         | USART1_TX                          | USART1_RX                                        | USART2_RX                            | USART2_TX            |

| 0011     | -         | I2C3_TX                 | I2C3_RX                                           | I2C2_TX <sup>(3)</sup>             | I2C2_RX <sup>(3)</sup>                           | I2C1_TX                              | I2C1_RX              |

| 0100     | TIM2_CH3  | TIM2_UP                 | TIM16_CH1<br>TIM16_UP                             | -                                  | TIM2_CH1                                         | TIM16_CH1<br>TIM16_UP                | TIM2_CH2<br>TIM2_CH4 |

| 0101     | -         | TIM3_CH3 <sup>(2)</sup> | TIM3_CH4 <sup>(2)</sup><br>TIM3_UP <sup>(2)</sup> | TIM7_UP.<br>DAC_CH2 <sup>(5)</sup> | QUADSPI                                          | TIM3_CH1 <sup>(2)</sup><br>TIM3_TRIG | -                    |

| 0110     | -         | -                       | TIM6_UP<br>DAC_CH1                                | -                                  | -                                                | -                                    | -                    |

| 0111     | -         | TIM1_CH1                | TIM1_CH2                                          | TIM1_CH4<br>TIM1_TRIG<br>TIM1_COM  | TIM15_CH1<br>TIM15_UP<br>TIM15_TRIG<br>TIM15_COM | TIM1_UP                              | TIM1_CH3             |

### **DMA Channel Configuration Register**

#### 11.6.3 DMA channel x configuration register (DMA\_CCRx)

Address offset: 0x08 + 0x14 \* (x - 1), (x = 1 to 7)

Reset value: 0x0000 0000

The register fields/bits MEM2MEM, PL[1:0], MSIZE[1:0], PSIZE[1:0], MINC, PINC, and DIR

are read-only when EN = 1.

The states of MEM2MEM and CIRC bits must not be both high at the same time.

| 31   | 30          | 29      | 28   | 27   | 26     | 25   | 24     | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|------|-------------|---------|------|------|--------|------|--------|------|------|------|------|------|------|------|------|

| Res. | Res.        | Res.    | Res. | Res. | Res.   | Res. | Res.   | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

|      |             |         |      |      |        |      |        |      |      |      |      |      |      |      |      |

| 15   | 14          | 13      | 12   | 11   | 10     | 9    | 8      | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| Res. | MEM2<br>MEM | PL[1:0] |      | MSIZ | E[1:0] | PSIZ | E[1:0] | MINC | PINC | CIRC | DIR  | TEIE | HTIE | TCIE | EN   |

|      | rw          | rw      | rw   | rw   | rw     | rw   | rw     | rw   | rw   | rw   | rw   | rw   | rw   | rw   | rw   |

#### **DMA Channel Selection Register**

#### 11.6.7 DMA channel selection register (DMA\_CSELR)

Address offset: 0xA8

Reset value: 0x0000 0000

This register is used to manage the mapping of DMA channels as detailed in *Section 11.3.2: DMA request mapping*.

| 31   | 30                | 29   | 28   | 27 | 26  | 25       | 24 | 23       | 22 | 21       | 20 | 19       | 18 | 17 | 16 |

|------|-------------------|------|------|----|-----|----------|----|----------|----|----------|----|----------|----|----|----|

| Res. | Res.              | Res. | Res. |    | C7S | [3:0]    |    | C6S[3:0] |    |          |    | C5S[3:0] |    |    |    |

|      |                   |      |      | rw | rw  | rw       | rw | rw       | rw | rw       | rw | rw       | rw | rw | rw |

| 15   | 14                | 13   | 12   | 11 | 10  | 9        | 8  | 7        | 6  | 5        | 4  | 3        | 2  | 1  | 0  |

|      | C4S[3:0] C3S[3:0] |      |      |    |     | C2S[3:0] |    |          |    | C1S[3:0] |    |          |    |    |    |

| rw   | rw                | rw   | rw   | rw | rw  | rw       | rw | rw       | rw | rw       | rw | rw       | rw | rw | rw |

### DMA Channel – Number of Data to Transfer Register

#### 11.6.4 DMA channel x number of data to transfer register (DMA\_CNDTRx)

Address offset: 0x0C + 0x14 \* (x - 1), (x = 1 to 7)

Reset value: 0x0000 0000

| 31   | 30        | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|------|-----------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Res. | Res.      | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. |

|      |           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 15   | 14        | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|      | NDT[15:0] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

|      |           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

### **DMA Stream Peripheral Address Register**

#### 11.6.5 DMA channel x peripheral address register (DMA\_CPARx)

Address offset: 0x10 + 0x14 \* (x - 1), (x = 1 to 7)

Reset value: 0x0000 0000

| 31 | 30        | 29 | 28 | 27 | 26 | 25 | 24 | 23     | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|-----------|----|----|----|----|----|----|--------|----|----|----|----|----|----|----|

|    | PA[31:16] |    |    |    |    |    |    |        |    |    |    |    |    |    |    |

| rw | rw        | rw | rw | rw | rw | rw | rw | rw     | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14        | 13 | 12 | 11 | 10 | 9  | 8  | 7      | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    |           |    |    |    |    |    | PA | [15:0] |    |    |    |    |    |    |    |

| rw | rw        | rw | rw | rw | rw | rw | rw | rw     | rw | rw | rw | rw | rw | rw | rw |

### DMA Channel - Memory address register

#### 11.6.6 DMA channel x memory address register (DMA\_CMARx)

Address offset: 0x14 + 0x14 \* (x - 1), (x = 1 to 7)

Reset value: 0x0000 0000

| 31 | 30        | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    | MA[31:16] |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| rw | rw        | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

| 15 | 14        | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    | MA[15:0]  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| rw | rw        | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw | rw |

#### Summary

- DMA enables efficient and low-latency access between memory and peripherals

- Need to configure DMA controller, then configure DMA requests from the peripheral (timer, USART, SPI, etc.)

- Use interrupts to handle and reset flags as necessary