# Multiple-Input Relay Design for More Compact Implementation of Digital Logic Circuits

Jaeseok Jeon, Louis Hutin, Ruzica Jevtić, Nathaniel Liu, Yenhao Chen, Rhesa Nathanael, Wookhyun Kwon, Matthew Spencer, Elad Alon, Borivoje Nikolić, and Tsu-Jae King Liu

*Abstract*—Multiple-input relays are proposed to enable more compact implementation of digital logic circuits, and the first functional prototypes are presented. A relay with three equally sized input electrodes is demonstrated to perform various threeinput logic functions, with a delay that can be well predicted by a lumped-parameter model. Relays with differently sized input electrodes can be used to perform more complex functions. A flash-type analog-to-digital converter is presented as one example.

Index Terms—MEMS, multiple inputs, NEMS, relay.

# I. INTRODUCTION

ANOELECTROMECHANICAL relay technology has been proposed as a potential solution to overcome the fundamental energy-efficiency limit of CMOS technology, because it offers the ideal characteristics of zero OFF-state leakage current and abrupt on/off switching behavior which provide for zero static power consumption and aggressive supply voltage  $(V_{DD})$  scaling [1], [2]. Various digital integrated circuit (IC) building blocks (logic, memory, and clocking structures) implemented purely with microelectromechanical relays have been demonstrated recently [3], [4]. Due to the large ratio between the mechanical (switching) delay and the electrical (capacitive charging) delay of a relay, an optimized relay-based IC design should comprise a single-stage complex logic gate between latches, so that the time required to perform any digital logic operation is essentially one mechanical delay [2]. Relay designs that incorporate multiple input (gate) electrodes and multiple pairs of output [source/drain (S/D)] electrodes enable more compact implementation of digital ICs at no incremental process cost. To illustrate this point, a generic n-input digital

Manuscript received November 1, 2011; accepted November 18, 2011. Date of publication January 9, 2012; date of current version January 27, 2012. This work was supported by the DARPA/MTO NEMS Program. The work of R. Jevtić was supported by Marie Curie International Outgoing Fellowship from the 7th European Community Framework Program. The review of this letter was arranged by Editor X. Zhou.

J. Jeon is with the Department of Electrical and Computer Engineering, Rutgers, The State University of New Jersey, Piscataway, NJ 08854-8058 USA (e-mail: jaeseok.jeon@rutgers.edu).

L. Hutin, R. Jevtić, Y. Chen, R. Nathanael, W. Kwon, M. Spencer, E. Alon, B. Nikolić, and T.-J. K. Liu are with the Department of Electrical Engineering and Computer Sciences, University of California Berkeley, Berkeley, CA 94720-1770 USA (e-mail: lhutin@eecs.berkeley.edu; ruzica@ eecs.berkeley.edu; ychen@eecs.berkeley.edu; rhesa@eecs.berkeley.edu; whkwon10@eecs.berkeley.edu; mespence@eecs.berkeley.edu; elad@eecs. berkeley.edu; bora@eecs.berkeley.edu; tking@eecs.berkeley.edu).

N. Liu is with Mission San Jose High School, Fremont, CA 94539 USA (e-mail: liu.nathaniel@gmail.com).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2011.2177436

VDD [1] VDD [2] Input [1] Pull-Up Relay Input [n] VDD [1] VDD [2] Pull-Up Relay Output [1] Output [2] Vss [1] VDD [2]

Fig. 1. Generic complementary-relay combinational logic circuit.

logic gate comprising only two relays is shown in Fig. 1. The "pull-up" relay connects the output to the power supply when it is turned on, whereas the "pull-down" relay connects the output to ground when it is turned on. Each input signal is connected to one input electrode of the pull-up relay and also to one input electrode of the pull-up relay and also to one input electrode of the pull-down relay, and only one of these relays is on at any given time, i.e., they operate in a complementary manner. Note that each relay can comprise multiple pairs of S/D electrodes, to provide for greater functionality, e.g., output signals at various voltage levels (as indicated in the figure) or differential output signals. In this letter, the first functional prototype multiple-input relays are presented.

## II. MULTIPLE-INPUT RELAY DESIGN

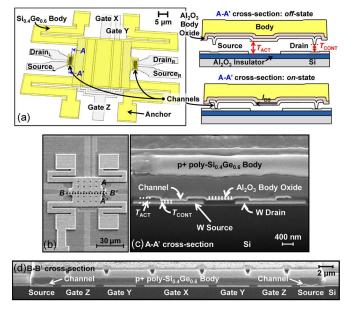

Fig. 2(a) shows the structure and operation of a prototype three-input two-output relay design: In the OFF state, an immeasurably low leakage current flows because an air gap (of thickness  $T_{\rm CONT}$ ) separates the channels from the pairs of S/D electrodes on each side. As the voltage applied to the gate electrode(s) increases beyond a threshold "pull-in" voltage  $(V_{\rm PI})$ , the relay turns on abruptly, because the attractive electrostatic force between the gate electrode(s) and the movable body electrode brings the channels (attached underneath the body electrode via an insulating oxide layer) into contact with the S/D electrodes

$$V_{\rm PI} \propto \sqrt{\frac{k T_{\rm ACT}^3}{\varepsilon_0 A}} \tag{1}$$

where k is the spring constant of the movable structure,  $T_{ACT}$  is the as-fabricated actuation gap thickness,  $\varepsilon_0$  is the dielectric permittivity of air, and A is the gate-to-body overlap area.

Fig. 2. Three-input two-output relay structure. (a) Three-dimensional schematic, (b) plan-view SEM of an unreleased device, (c) cross-sectional SEM (X-SEM) along A-A' in (b), and (d) X-SEM along B-B' in (b).  $T_{\rm BODY} = 900$  nm,  $T_{\rm BODY.OXIDE} = 45$  nm,  $T_{\rm CHANNEL} = 50$  nm,  $T_{\rm ACT}$  (as-designed) = 180 nm,  $T_{\rm CONT}$  (as-designed) = 90 nm,  $T_{\rm GATE} = T_{\rm SOURCE} = T_{\rm DRAIN} = 60$  nm, and  $T_{\rm SUBSTRATE.INSULATOR} = 80$  nm. The gate electrodes—Gate X at the center, Gate Z at the edges, and Gate Y in-between Gates X and Z—are equally sized (each with an area of 288  $\mu$ m<sup>2</sup> underneath the movable body electrode). Thin films of Pt and Ir were deposited over the poly-Si<sub>0.4</sub>Ge<sub>0.6</sub> body electrode for protection during the focused ion beam cutting process for the X-SEMs.

A CMOS-compatible (peak substrate temperature < 410 °C) surface-micromachining process [5] was used to fabricate the relays in this work. The scanning electron microscopy (SEM) images of a fabricated three-input two-output relay are shown in Fig. 2(b)–(d).

#### **III. RESULTS AND DISCUSSION**

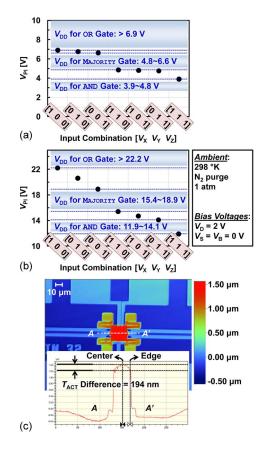

Finite-element method (FEM) simulations were performed to provide guidance for relay design, targeting  $\sim$ 5-V  $V_{\rm DD}$  for AND operation [Fig. 3(a)]. Since the voltage level required to turn on the relay increases as the number of driven gate electrodes decreases (since the effective gate-to-body overlap area A increases) AND, MAJORITY  $(X \bullet Y + Y \bullet Z + X \bullet Z)$  and OR functions can be achieved with the same relay structure by adjusting the input voltage level (i.e.,  $V_{DD}$ ). Fig. 3(b) shows that the measured values of  $V_{\rm PI}$  are much higher than the simulated values. Physical analysis [Fig. 3(c)] indicates that the actuation gap  $(T_{ACT})$  is much larger than designed, due to the effect of a negative strain gradient within the structural (body) layer. The measured value of  $V_{\rm PI}$  for the case where the input signals are applied to all three gates (input combination [1 1 1], where "1"  $\equiv V_G$ ), i.e., "triple-gate" operation, is  $\sim 3 \times$  larger than the simulated  $V_{\rm PI}$ . This is consistent with the interferometry-based measurements which indicate that  $T_{ACT}$  is larger than designed by  $\sim 2 \times$ , since  $V_{\rm PI} \propto T_{\rm ACT}^{1.5}$ .

The measured  $V_{\rm PI}$  for the case where the input signal is applied only to Gate X (input combination [1 0 0]) is larger than those for the cases where the input signal is applied only to Gate Y or Gate Z (input combination [0 1 0] or [0 0 1], respectively)

Fig. 3. Comparison of simulation and measurement results for a three-input relay. (a) FEM simulations [6] of  $V_{\rm PI}$ , for various combinations of input signals, for the three-input relay. "1"  $\equiv V_G$ . (b) Measured  $V_{\rm PI}$  values. "1"  $\equiv V_G$ . (c) White-light interferometry topograph of the fabricated relay.  $T_{\rm ACT}$  at the body center is 374 nm, which is roughly twice as large as designed.

because  $T_{ACT}$  is larger at the center than at the edge of the body due to the convex shape of the body electrode.

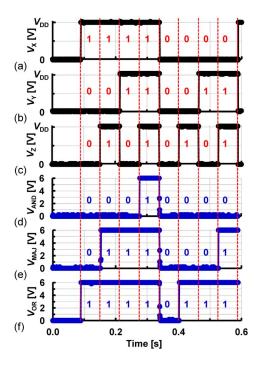

The versatility of the three-input relay design is demonstrated in Fig. 4, which shows the measured waveforms for a threeinput relay with drain electrodes connected to a 6-V power supply and source electrodes connected to an oscilloscope with 1-M $\Omega$  internal resistance: When the input voltage range (corresponding to  $V_{DD}$ ) is 10 V, the relay performs the AND function; when it is increased to 13 V, the relay performs the MAJORITY function; and when it is increased to 18 V, the relay performs the OR function.

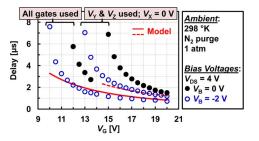

Fig. 5 shows the measured three-input-relay turn-on delay  $(t_{\text{DELAY}})$  as a function of the driving gate voltage  $(V_G)$ , for double- and triple-gate operations.  $t_{\text{DELAY}}$  decreases with increasing gate overdrive, and triple-gate operation is faster, due to larger electrostatic force between the gates and the body. A negative body bias also improves  $t_{\text{DELAY}}$  because it serves to reduce  $T_{\text{ACT}}$  and  $T_{\text{CONT}}$  in the OFF state, so that the body moves a shorter distance to switch the relay on. A first-order lumped-parameter model predicts  $t_{\text{DELAY}}$  to be inversely proportional to  $V_G^2$  [7]

$$t_{\rm DELAY} = \frac{27V_{\rm PI}}{4\omega_O \cdot Q \cdot V_G^2}.$$

(2)

A reasonable fit to the measured data is achieved with the following parameter values: quality factor Q = 0.5,

Fig. 4. Measured waveforms obtained using a single three-input relay with drain electrodes connected to a 6-V power supply and source electrodes tied together to form the logic gate output node connected to the oscilloscope (1-MΩ resistance to ground). The body is biased at -2 V. The measurements were made at room temperature and atmospheric pressure, under N<sub>2</sub> purge. (a) INPUT X signal (to "Gate X"). (b) INPUT Y signal (to "Gate Y"). (c) INPUT Z signal (to "Gate Z"). (d) AND output waveform for  $V_{\rm DD} = 10$  V. (e) MAJORITY gate (X • Y + Y • Z + X • Z) output waveform for  $V_{\rm DD} = 18$  V.

Fig. 5. Measured turn-on delay of a three-input relay as a function of the input voltage, for various values of body bias. A lumped-parameter model (lines) can be reasonably fit to the experimental data.

resonance frequency  $\omega_O = 5.4$  MHz, and  $V_{\rm PI} = 14.1$  or 11.9 V for double- or triple-gate operation [refer to Fig. 3(c)]. The supply voltage ( $V_{\rm DD} > V_{\rm PI}$ ) must be chosen properly to meet a specific switching delay requirement and to mitigate variations in  $V_{\rm PI}$  (refer to Fig. 3).

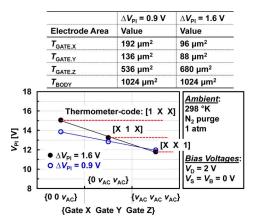

More complex logic functions can be achieved by adjusting the areas of the input electrodes to give them different weights. (The relative weight of an input gate is determined by its relative gate-to-body overlap area, as compared with the other input electrodes.) For example, by sizing the gate electrodes appropriately, three 3-input relays can be used to implement a flash-type analog-to-digital converter (ADC), as shown in Fig. 6: The switching voltages for single-gate (most significant bit), double-gate, and triple-gate [least significant bit (LSB)] operations decrease linearly to properly decode an analog input signal level ( $v_{ac}$ ). For instance, if  $v_{ac}$  is between 11.7 and 13.3 V, only the LSB relay (with  $v_{ac}$  driving all three gates)

Fig. 6. Measured linearly increasing  $V_{\rm PI}$  of a three-input relay with differently sized gates for ADC application.

turns on; the other two relays (with  $v_{\rm ac}$  driving only the two smallest gates or with  $v_{\rm ac}$  driving only the smallest gate) do not turn on, so that the thermometer code [0 0 1] is generated.

## **IV. CONCLUSION**

Multiple-input relays have been proposed to implement digital logic more compactly than single-input relays. (Although a multiple-input relay has a larger footprint than a single-input relay for the same input voltage range, the reduction in device count is advantageous because of the significant area required for the suspension beams and anchors and for routing of the S/D electrodes.) A relay with three equally sized input electrodes can perform various three-input logic functions, depending on the input voltage level, with a delay that can be well predicted by a lumped-parameter model. Relays with differently sized input electrodes can be used to perform more complex functions, such as a flash-type ADC.

#### ACKNOWLEDGMENT

The relays were fabricated in the Marvell Nanofabrication Laboratory, University of California, Berkeley.

#### REFERENCES

- K. Akarvardar, D. Elata, R. Parsa, G. C. Wan, K. Yoo, J. Provine, P. Peumans, R. T. Howe, and H.-S. P. Wong, "Design considerations for complementary nano-electro-mechanical logic gates," in *IEDM Tech. Dig.*, 2007, pp. 299–302.

- [2] F. Chen, H. Kam, D. Marković, T.-J. K. Liu, V. Stojanovic, and E. Alon, "Integrated circuit design with NEM relays," in *Proc. IEEE/ACM Int. Conf. Comput.-Aided Des. Tech. Dig.*, 2008, pp. 750–757.

- [3] F. Chen, M. Spencer, R. Nathanael, C. Wang, H. Fariborzi, A. Gupta, H. Kam, V. Pott, J. Jeon, T.-J. K. Liu, D. Marković, V. Stojanović, and E. Alon, "Demonstration of integrated micro-electro-mechanical (MEM) switch circuits for VLSI applications," in *Proc. Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2010, pp. 150–151.

- [4] H. Fariborzi, F. Chen, R. Nathanael, J. Jeon, T.-J. K. Liu, and V. Stojanović, "Design and demonstration of micro-electro-mechanical relay multipliers," in *Proc. Asian Solid-State Circuits Conf.*, Jeju, Korea, Nov. 2011.

- [5] R. Nathanael, V. Pott, H. Kam, J. Jeon, and T.-J. K. Liu, "4-terminal relay technology for complementary logic," in *IEDM Tech. Dig.*, 2009, pp. 223–226.

- [6] CoventorWare 2008 Ref. Manual, Coventor, Inc., Cary, NC, 2008.

- [7] G. M. Rebeiz, *RF MEMS Theory, Design, and Technology*. Hoboken, NJ: Wiley, 2003, pp. 66–69.