## **Digital Design and Computer Architecture (E85)**

K. Wang & J. Spjut

Fall 2012

## Midterm

"There are 10 kinds of people in the world – those who understand binary and those who don't."

This is a closed-book closed-notes exam. You are permitted a calculator and one 8.5x11" sheet of paper with notes. You may have notes on both sides of the single 8.5x11" sheet.

You are allowed at most 1 hour and 30 minutes to take the exam.

Along side each question, the number of points is written in brackets. The entire exam is worth 100 points. Plan your time accordingly. All work and answers should be written directly on this examination booklet. Use the backs of pages if necessary. Write neatly; illegible answers will be marked wrong. **Show your work** for partial credit.

| Name: | Aswer | Keys |  |

|-------|-------|------|--|

|       |       |      |  |

This is a closed-book closed-notes exam. You are permitted a calculator and one 8.5x11" sheet of paper with notes. You may have notes on both sides of the single 8.5x11" sheet.

You are allowed at most 1 hour and 30 minutes to take the exam.

Along side each question, the number of points is written in brackets. The entire exam is worth 100 points. Plan your time accordingly. All work and answers should be written directly on this examination booklet. Use the backs of pages if necessary. Write neatly; illegible answers will be marked wrong. **Show your work** for partial credit.

| Do Not Write B | elow I his Point |  |

|----------------|------------------|--|

| Page 3:        | /12              |  |

| Page 4:        | /12              |  |

| Page 5:        | /24              |  |

| Page 6:        | /13              |  |

| Page 7:        | /13              |  |

| Page 8:        | /10              |  |

| Page 9:        | /8               |  |

| Page 10:       |                  |  |

| Total:         | /100             |  |

1. [24 pts] For the Boolean equation

$$Y = (A \oplus B) C + \overline{A} B \overline{C} + \overline{A} \overline{B} C$$

6p+5 (a) Show the truth table for Y as a function of inputs A, B, and C.

|          | A | B | C | Y  |

|----------|---|---|---|----|

| -        | 0 | 0 | 0 | 0  |

|          | 0 | 0 | 1 | -1 |

| <b>→</b> | 0 | 1 | 0 | 1  |

|          | 0 | ĺ | ١ | 1  |

|          | 1 | 0 | G | 0  |

|          | 1 | 0 | 1 | 1  |

|          | 1 | 1 | 0 | 0  |

|          | 1 | 1 | 1 | 0  |

6 pts (b) Simply the Boolean equation for Y as a function of inputs A, B, and C.

$$C \longrightarrow OO \bigcirc O \bigcirc O \bigcirc O$$

$$C \longrightarrow OO \bigcirc O$$

$$C \longrightarrow OO$$

1 (cont.)

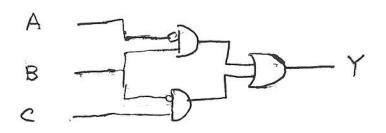

6 pts (c) Show the gate schematic for inputs A, B, and C and out Y. Use the minimum numbers of AND and OR gates.

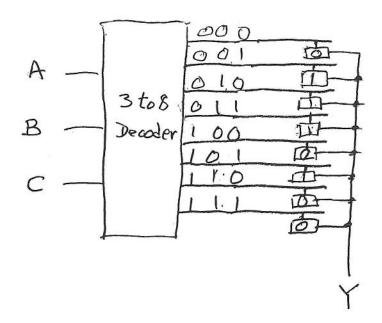

6 pts (d) Show a lookup table (LUT) implementation of Y as a function of inputs A, B, and C.

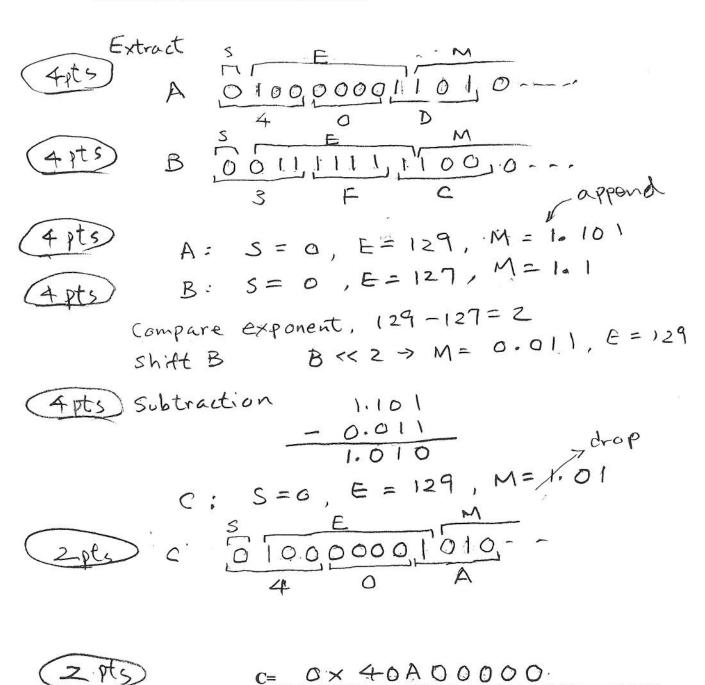

| 2)  | [24pts] | Perform | floating | point | subtraction | 1 C= A - | - B i | n 32-bit | <b>IEEE 754</b> | floating | point |

|-----|---------|---------|----------|-------|-------------|----------|-------|----------|-----------------|----------|-------|

| for | rmat    |         |          |       |             |          |       |          |                 |          |       |

| 1 bit | 8 bits   | 23 bits  |       |

|-------|----------|----------|-------|

|       |          |          |       |

| Sign  | Exponent | Mantissa | 0.000 |

where A = 0x40D000000

B = 0x3FC00000

Write the answer C in hexadecimal format.

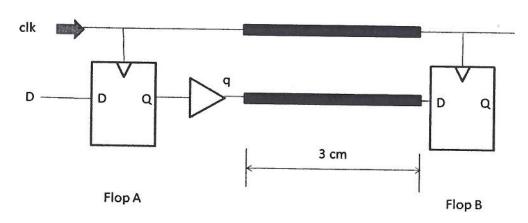

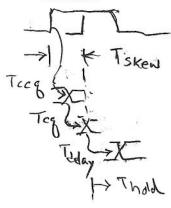

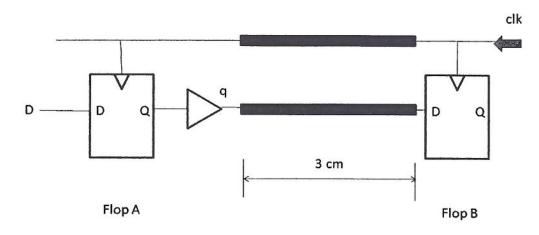

3. [26 pts] In a PCB board design, the output of flip-flop A is buffered and the output signal q is driven 3 cm to the input of flip-flop B. The clk signal and q are carefully laid out next to each other, both traveling with the same speed of 1.5 x 10<sup>8</sup> m/sec. The flip-flop and buffer timing parameters are given in Tables 1 and 2 respectively.

Table 1 Flip-Flop Timing Parameters

| Tpcq   | 50 ps |

|--------|-------|

| Tecq   | 10 ps |

| Tsetup | 50 ps |

| Thold  | 20 ps |

Table 2 Buffer Timing Parameters

| Tpq | 400 ps |

|-----|--------|

| Tcq | 200 ps |

Figure 1

(a) If clk and q travel in the same direction as shown in Figure 1, what is the maximum frequency that the clk can operate?

Page 6 of 10 210 > 20 yes

Therefore, no hold time proble

Figure 2

(c) If clk and q travel in the opposite direction as shown in Figure 2, what is the maximum frequency that the clk can operate?

$$T_c = T_{pc}g + T_{pg} + T_{delay} + T_{setup} + T_{skew}$$

$$= 50 + 400 + 200 + 50 + 200$$

$$= 900 \cdot PS = 0.9 \text{ nS}$$

$$f_{max} = \frac{1}{T_c} = 1.11 \text{ GHz}$$

(7 Pts) (d) Is there a hold time problem? Justify your answer.

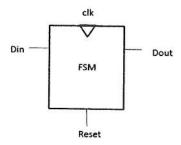

4.[26] A NRZ1 generator for a input data sequence of 1's and 0's is defined as follows:

- For each 0 in the input data sequence, the bit output is the same as the previous bit output.

- For each 1 in the in the input data sequence, the bit output is the complement of the previous output.

For example:

Data input sequence 0 1 1 1 0 0 1 0

Data output sequence 0 1 0 1 1 1 0 0

Assume output is reset to 0 and the input sequence starts at 0.

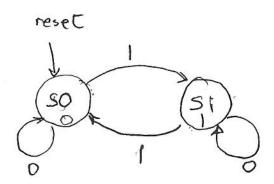

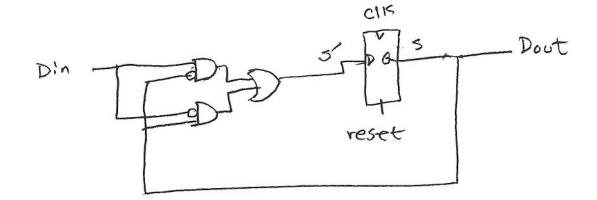

Design a FSM that generates the output sequence Dout from the input data sequence Din as shown in Figure 4.

Figure 4

(a) Show state transition diagram.

(b) Show gate schematic for the FSM design.

Define

transition table

8pts

(c) Write a HDL description of the FSM design using system Verilog.

```

module NRZI (input logic din, reset, CIK)

output logic dout);

typedefine enum logic [0] { so, sif state type;

Statetype State, next state;

always-ff @ (posedge clk or reset);

if (reset) state (= 50;

else State < mext state;

Il next state log: c

always-comb

case (state)

50: if (ndih) next state = 50;

dse next state = 51;

SI o if (rdin) nextstate = SI;

nextstate = SO;

else

nextestate = 50;

endcase default:

1/output logic

assign dout = (state == 50) ? 0:1;

endmadule

```