# E85: Digital Design and Computer Architecture

J. Spjut Fall 2014

Lab 1: Full Adder

#### Introduction

In this lab you will design a simple digital circuit called a *full adder*. Along the way, you will learn to use the Altera field-programmable gate array (FPGA) tools to enter a schematic, simulate your design, and download your design onto a chip. You will also build your adder on a breadboard using discrete chips to get a more tactile sense of digital logic.

After completing the lab, you are required to turn in something from each part. Refer to the "What to Turn In" section at the end of this handout before beginning the lab.

The computer-aided design (CAD) tools required for this class are installed in the E85 lab (Parsons B183). If you would like to work from the convenience of your own computer, you can download the Altera Quartus II Web Edition software from the web. Note that the latest version to support the Cyclone 2 is version 13.0 (which is what is installed on the lab computers). Some computers may have different versions of Quartus II installed. Be sure you are using the "Web Edition" for the version you use to prevent running into licensing issues.

# **Background: Adders**

An adder, not surprisingly, is a circuit whose output is the binary sum of its inputs. Since adders are needed to perform arithmetic, they are an essential part of any computer. The full adder will be an integral part of the microprocessor that you design in later labs.

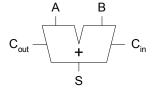

A full adder has three inputs  $(A, B, C_{in})$  and two outputs  $(S, C_{out})$ , as shown in Figure 1. Inputs A and B each represent 1-bit binary numbers that are being added, and S represents a bit of the resulting sum.

Figure 1. Full adder

The  $C_{\rm in}$  (carry in) and  $C_{\rm out}$  (carry out) signals are used when adding numbers that are more than one bit long. To understand how these signals are used, consider how you would add the binary numbers 101 and 001 by hand:

As with decimal addition, you first add the two least significant bits. Since 1+1=10 (in binary), you place a zero in the least significant bit of the sum and carry the 1. Then you add the next two bits with the carry, and place a 1 in the second bit of the sum. Finally, you add the most significant bits (with no carry) and get a 1 in the most significant bit of the sum.

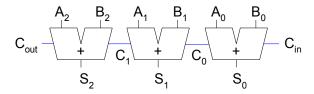

When a sum is performed using full adders, each adder handles a single column of the sum. Figure 2 shows how to build a circuit that adds two 3-digit binary numbers using three full adders. The  $C_{\text{out}}$  for each bit is connected to the  $C_{\text{in}}$  of the next most significant bit. Each bit of the 3-bit numbers being added is connected to the appropriate adder's inputs and the three sum outputs ( $S_{2:0}$ ) make up the full 3-bit sum result.

Figure 2. 3-bit adder

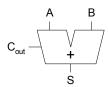

Note that the rightmost  $C_{\rm in}$  input is unnecessary, since there can never be a carry into the first column of the sum. This would allow us to use a half adder for the first bit of the sum. A half adder is similar to a full adder, except that it lacks a  $C_{\rm in}$  and is thus simpler to implement. To save you design time, however, you will only build a full adder in this lab.

Figure 3. Half adder

## 1. Design

A partially completed truth table for a full adder is given in Table 1. The table indicates the values of the outputs for every possible input, and thus completely specifies the operation of a full adder. As is common, the inputs are shown in binary numeric order. The values for S (sum) are given, but the  $C_{\text{out}}$  (carry out) column is left blank. Complete the table by filling in the correct values for  $C_{\text{out}}$  so that adders connected as in Figure 2 will perform valid addition.

| Inputs            |   |   | Outputs |   |

|-------------------|---|---|---------|---|

| $C_{\mathrm{in}}$ | В | A | Cout    | S |

| 0                 | 0 | 0 |         | 0 |

| 0                 | 0 | 1 |         | 1 |

| 0                 | 1 | 0 |         | 1 |

| 0                 | 1 | 1 |         | 0 |

| 1                 | 0 | 0 |         | 1 |

| 1                 | 0 | 1 |         | 0 |

| 1                 | 1 | 0 |         | 0 |

| 1                 | 1 | 1 |         | 1 |

Table 1. Partially completed truth table for full adder

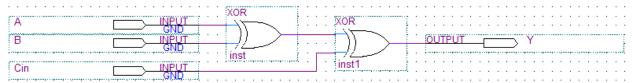

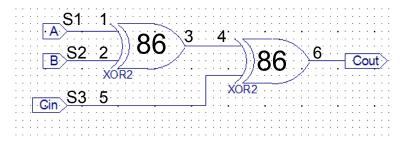

From the truth table, we now want to implement our design using logic gates. The sum output (S) can be produced from the inputs by connecting two 2-input XOR gates as shown in Figure 4. You should convince yourself that this circuit produces the outputs for S as given in the table.

Figure 4. Schematic for sum logic

Using only two-input logic gates (AND, OR, XOR) and inverters (NOT), design a circuit that takes A, B, and  $C_{\rm in}$  as its inputs and produces the  $C_{\rm out}$  output. Try to use the fewest number of gates possible. Sketch your schematic.

#### 2. Schematic

Now that you know how to produce both the sum (S) and carry out  $(C_{out})$  outputs using simple logic gates, you will now construct a working full adder circuit using real hardware. One way to test your circuit before building it in hardware is to enter the schematic representation of your logic into a software package. You can then simulate the circuit and test that it works the way you expect it to. Some software packages are then capable of programming the schematic into an integrated circuit. This semester we will be using the Altera Quartus II 13.0 Web Edition software for these purposes. The Quartus software is a powerful and popular commercial suite of applications used by hardware designers.

First, you will learn how to start a new project. Start the Quartus software from the Start menu. If asked about the look and feel, choose Quartus II.

In the Getting Started Window, click on Create a New Project. In the New Project Wizard, set the working directory to a good place in your Charlie home directory. For example, if your Charlie directory is mapped to the H drive, choose H:\e85\lab1\_xx, where xx are your initials. Name the project lab1\_xx. Make sure there are no spaces or unusual characters in the path or file name; the tools may complain or silently misbehave if it has trouble with the file name. If prompted about whether to create the directory, say Yes.

Click Next to go to the Add Files page. You won't be using preexisting files, so click Next again to the Family & Device Settings to select a chip. You'll be using the Altera DE2 development board, which contains a Cyclone II EP2C35F672C6 FPGA. Set the family to Cyclone II. Scroll down and select the device (EP2C35F672C6) from the list of Available Devices. EP2C indicates the Cyclone II family of chip. The 35-series is a medium-sized chip with 33,216 (approximately 35k) logic elements. F672 indicates a fine-pitch 672-pin ball grid array package. C6 indicates a commercial-grade part (rated for operating temperatures of  $0-85\,^{\circ}$ C) and 6 is the slowest (and cheapest) speed grade for this part.

Click Next to go to the EDA (Electronic Design Automation) Tool Settings. Set the Design Entry/Synthesis Tool name to ViewDraw using EDIF (Electronic Design Interchange Format) and the Simulation tool to Modelsim using Verilog HDL. Click Next and Finish to create your new project.

The Quartus window will open in a moment. You may wish to maximize the window. You will see three main panes, as shown in Figure 5 (and can bring them up from the View  $\rightarrow$  Utility Windows menu if you accidentally close one):

- **Project Navigator:** Lists the current project's sources file and the chip in use.

- **Tasks:** Lists the processes to perform on the source selected in the Sources pane. For example, we will use this pane later to simulate your completed schematic.

- **Messages:** Lists the output of current processes, errors, and warning at the bottom of the screen. Keep an eye on these messages; important warnings appear here.

Figure 5. Quartus II window

We will describe some of the options for using these resources, but we also recommend exploring these resources on your own to become familiar with Quartus' capabilities. Use the Help menu for additional information.

Quartus has a basic and strikingly ugly schematic editor that we will use. It is not particularly sophisticated because designers today primarily use hardware description languages (HDLs) instead of schematics. However, understanding schematics is an important first step to mastering HDLs.

Create a new schematic by choosing File → New and selecting Block Diagram / Schematic File, and click OK. A new schematic window named Block1.bdf will appear.

First, place your logic gates. Click on the Symbol Tool icon (shaped like an AND gate). Expand the list of libraries in the upper left of the Symbol window by clicking on the arrow icons Look under primitives  $\rightarrow$  logic and choose xor. Click OK, then click twice on the schematic window to place two xor gates. Leave some room between the gates to draw a wire later. Press the Esc key or right click and choose Cancel to get out of the placement mode.

Click on the Symbol Tool again and choose primitives  $\rightarrow$  pin  $\rightarrow$  input. Place three input pins on the left side. Leave some space between the pins and the gates so that you can wire them together later. Then choose an output pin and place it on the right. Double click on one of the input pins and change its name to A. Leave the default value unchanged at VCC. Rename the other inputs to B and Cin. Rename the output to S.

Use the Orthogonal Node Tool ( ) to wire the gates together. Click and drag to connect the pins to gates and the two gates together. At this point, your schematic should resemble Figure 4.

It's a good idea to click on the wire between the two XOR gates and give it a unique name such as *n1* or *mid* in case you need to debug later. (If you are using version 10 or higher, you can name a wire by right clicking on the wire, selecting Properties, and adding the name).

If you need to make corrections, use the Selection Tool to grab and move gates or wires. Zoom in and out by using the View menu or holding the Ctrl key while turning the mouse wheel. Use delete and undo as necessary.

Choose File  $\rightarrow$  Save and save your schematic as lab1 xx.bdf.

You are now ready to complete your schematic of the full adder by drawing the logic for  $C_{\text{out}}$  that you designed in Part 1. Draw the necessary logic gates and wires to complete the circuit. Use the existing input terminals for A, B, and Cin, and add an output terminal for Cout. The symbols you may use to draw your logic gates are as follows: and 2, and 3, or 2, or 3, not, and xor.

Remember, do not add a second set of input ports for A, B, and  $C_{\rm in}$ . Instead, note that you can connect multiple wires to the same input ports (or you can connect wires to other wires to create branches).

Select the Files tab in the Project Navigator pane to see a list of files of the project (presently just lab1 xx.bdf). If you need to reopen the file later, double-click on it here.

To check your design, click on Start Compilation in the Task pane (Processing -> Start Compilation). You'll see a compilation report indicating five pins and 2 logic elements. Review the warnings and errors carefully. You may get the following warnings that are harmless:

- Feature LogicLock only available with subscription.

- Ignored location or region assignments

- Found output pins without load capacitance

- Found invalid Fitter assignments

- Reserve All Unused Pins not specified

If you see other warnings or errors, track down their root cause before they lead you to grief later.

#### 3. Simulation

One motivation for drawing your full adder schematic in Quartus is that you can now use the software to simulate the operation of the circuit. It is a good idea to verify the correctness of your design before actually building the circuit in hardware. In this part of the lab, you will simulate the design using **ModelSim.** Be sure to use ModelSim-Altera 10.0d **Starter Edition** to avoid licensing errors.

ModelSim expects a description of a circuit in a hardware description language (HDL) such as Verilog. To convert your schematic to Verilog, open the schematic and choose File  $\rightarrow$  Create / Update  $\rightarrow$  Create HDL Design File for Current File. Choose Verilog HDL. Your file should be written to lab1 xx.v. Watch for and correct any warnings or errors that arise.

Now fire up ModelSim SE 6.6b from the Windows start menu. Maximize the ModelSim window when it opens. If prompted, you may wish to associate file types with ModelSim but do not want to use Jumpstart.

Choose File  $\rightarrow$  New  $\rightarrow$  Project. Name the project lab1\_xx and put it in the directory where you are working (e.g. H:/e85/lab1\_xx). Accept the default library name of "work." Then click "Add Existing File" and add lab1 xx.v.

You should see lab1\_xx.v in the ModelSim project pane. Double-click on it to view it. The file should list the inputs and outputs and the wires (using default names if you didn't name them yourself). It should then have a series of "assign" statements describing the gates. & indicates AND. | indicates OR. ^ indicates XOR. In future labs you will learn to write Verilog yourself.

Choose Compile → Compile All to compile the Verilog code into a form that ModelSim can simulate. Watch for and correct errors in the transcript pane. Then choose Simulate → Start Simulation. Click on Work to expand the library, and choose lab1\_xx as your module to simulate. Uncheck "enable optimization" because it sometimes hides information that is useful during debugging. Click Ok.

ModelSim will open more panes including sim and Objects that help you select signals for the waveform viewer. In the sim pane, be sure lab1\_xx is selected. In the objects window, you'll see all the inputs, outputs, and internal wires. Shift-click to select them all. Then right-click and choose Add  $\rightarrow$  To Wave  $\rightarrow$  Selected Signals. A Wave pane will pop up with the signals.

Now it is time to apply the inputs. In the transcript pane at the bottom, type

```

force A 0 force B 0 force Cin 0 run 100

```

This will set all three inputs to 0 and simulate for 100 ns. (Note that Verilog is case-sensitive; "A" and "a" are different.) You should see all the inputs and outputs at a low level in the Wave pane. Next, raise A:

```

force A 1 run 100

```

You'll see A rise. If your design is correct, S will also rise.

Continue with the six other patterns of inputs to check your truth table.

If you have errors, you may want to look at the internal nodes to track down the problem. Fix the schematic, then regenerate the Verilog file. Recompile and restart the simulation in ModelSim.

If the waveform is not visible, click on the + button in the top right corner of the "wave-default" pane to the right of the main ModelSim window (or choose View $\rightarrow$ Wave from the menu). Click the "Zoom Full" icon in the taskbar to see the whole waveform of the simulation results. You can also use the "Zoom In" and "Zoom Out" icons: Check and see that the output values (S and  $C_{out}$ ) are correct. If not, go back and fix your schematic and resimulate. When the output values are correct, you have a working full adder! Save an image of the waveform. Make sure the entire waveform is visible, select File $\rightarrow$ Export $\rightarrow$ Image..., and save the file. If needed, you can also print the waveform. Choose File $\rightarrow$ Print to print a copy of your waveforms to turn in. You can choose the start and end times in the bottom right of the print dialog box.

### 4. DE2 Board Implementation

Once your design simulates correctly, you may now close Modelsim and return to Quartus.

Your next goal is to download your circuit onto a DE2 board to test it on the FPGA. In hardware, particular pins on the FPGA will correspond to the inputs and outputs of your design. You'll need to assign the pins so that you can use switches to control the inputs and LEDs to display the outputs. Altera provides a file describing how the various circuits on the DE2 board are connected to the FPGA. To use this file, choose Assignments → Import Assignments. Set the file name to

$\verb|\Charlie.hmc.edu| Courses \\| Engineering \\| E85 \\| Labs \\| DE2\_pin\_assignments.csv|$

Open your schematic. Rename the pins to match the names on the board. Rename the inputs from A, B, and Cin to SW[0], SW[1], and SW[2], respectively. Rename the outputs S and Cout to LEDR[0] and LEDR[1], respectively. Save your schematic.

In the Tasks pane, recompile the design.

The DE2 boards should be all set up and you should have no reason to disconnect them this semester. However, you need to plug one in, follow the steps below:

- Connect the DE2 board to the computer using a USB cable. The cable should go into the leftmost USB jack on the board labeled BLASTER.

- Switch S9 should be in the RUN position.

Check that the board is turned on (press the red power button); the blue Power and Good LEDs should turn on.

Choose Tools → Programmer. Check that the Hardware Setup is set to USB-Blaster and the mode to JTAG. The file should be lab1\_xx.sof and the program/configure box should be checked. Click Start to download your design.

You may ignore the large number of warning messages related to the unused pins.

Toggle SW0, SW1, and SW2 through the eight possible patterns. Check that LEDR0 and LEDR1 display the correct sums!

If any of the boards aren't working correctly for you, try another station. If that works, label the board as bad and email the instructor with a note so that your classmates don't suffer the same issue and the problem gets fixed! ©

## 5. Breadboard Implementation

In the 1970's and 1980's, engineers built systems from many small-scale integration (SSI) chips that each contain a handful of logic gates. They connected the chips together with wires on a breadboard. This approach gives you more of a visceral feel for logic gates. Breadboarding remains a valuable skill for testing out circuits before you build your own printed circuit board.

In this part of the lab, you will implement your design in hardware using 74xx-series chips, commonly sold in 14-pin dual inline packages (DIPs). Each chip contains a number of logic gates. The inputs and outputs of the gates can be accessed through the chip pins, the metal legs on each side of the black plastic package. Section A.2 of *Digital Design and Computer*

Architecture has vital information about these chips, including the pinouts and how they should be used.

First, retrieve as many 74xx-series chips as you need to implement your 1-bit full adder. They are located in the black cabinet in the lab. Recall that each chip contains multiple gates. Wires and wirecutters are also located in the lab for your use. Build your circuit on the protoboard located next to each computer. You will likely want to print out your schematic and label your circuit, as shown in Figure 6 for the sum logic. The circuit could have used any of the four XOR gates on the 7486 chip. Label each gate with the chip you will be using (in this case, the 7486 chip). Label each input and output with the pin number that you will connect it to. S1, S2, and S3 indicate switches 1, 2, and 3 on the protoboard.

Figure 6. Example circuit schematic with pinout notations

Section A.7 of *Digital Design and Computer Architecture* explains how to place your chips on a breadboard and wire them together.

The protoboards in the lab have internal power supplies. On the top right corner of the protoboard is a red knob labeled '5 V'. It is internally connected to the top row of the breadboard. The black knob below it is labeled with the GND symbol and is connected to the row fourth from the top on the protoboard, as indicated by the white adjoining line.

After placing your chips on the protoboard, connect one vertical column to VDD and one vertical column to GND using wires. Note that the top half of each vertical column is inexplicably not connected to the bottom half. Either use wires to make the connection between the halves, or only use the top half. Now use short wires to connect power (VDD) and ground (GND) to your chips.

Use wires to connect the chips according to your 1-bit full adder design. Connect your inputs (A, B, and  $C_{\rm in}$ ) to the logic switches at the bottom of the protoboard (labeled "LOGIC SWITCHES"). Choose any of the switches,  $S_1$  -  $S_8$ . It doesn't matter which row you use. Be sure the black switch just above the input switches is switched up to +5, indicating they are 5 Volt inputs. Connect the outputs, S and  $C_{\rm out}$ , to LED's located in the "LOGIC INDICATORS" box on the top right of the protoboard. The red LED indicates that the output is HIGH (1), and the green LED indicates that the output is LOW (0). Be sure the switch just above the LEDs is switched up to +5 and that the switch below the LEDs is switched down to CMOS. These indicate which logic levels to use to turn on the LEDs.

After you have completed your circuit, toggle the inputs according to Table 1 and test that the outputs function correctly. If not, debug your circuit until it functions correctly. Sometimes,

connections on the breadboard can be loose or finicky. If the circuit is behaving suspiciously, it is helpful to check voltages with a multimeter and verify that they match your expectations.

It's possible to damage chips, especially by shorting an output to power or ground or another output. If your measurements reveal suspicious behavior, make sure that power and ground are attached to the chip. Disconnect all wires from the output. Apply known good inputs and check the output with

When your circuit works, you are all done. Congratulations on completing lab 1!

#### What to Turn In

You must submit an electronic copy of the following items via Sakai. Be sure to label each section and organize them in the following order. Messy or disorganized labs will lose points.

- 1. Please indicate how many hours you spent on this lab. This will be helpful for calibrating the workload for next time the course is taught.

- 2. Write a few sentences describing the purpose of this lab.

- 3. Include your completed truth table, including the values in the  $C_{\rm out}$  column.

- 4. Include the following figures:

- Your completed schematic, including the logic gates for both S and Cout. This can be produced using the File→Export feature in the Schematic Editor (you may need to select .bmp format).

- Your simulation of the full adder, including all inputs and outputs. This can be produced using the File > Export > Image... feature of the ModelSim Simulator.

- 5. Did your full adder on the DE2 board pass work for all eight possible inputs?

- 6. Did your full adder on the breadboard pass work for all eight possible inputs?

If you have suggestions for further improvements of this lab, you're welcome to include them at the end of your lab.