### **PIC32** Overview

E155

## Outline

PIC<sup>32</sup> Architecture

MIPS M4K Core

PIC<sup>32</sup> Peripherals

PIC<sup>32</sup> Basic Operations

Clock

# Microcontroller

- Approximately \$16B of microcontrollers were sold in 2011, and the market continues to grow by about 10% a year.

- Microcontrollers have become ubiquitious and nearly invisible, with an estimated 150 in each home and 50 in each automobile in 2010.

- The 8051 is a classic 8-bit microcontroller originally developed by Intel in 1980 and now sold by a host of manufacturers.

- Microchip's PIC16 and PIC18-series are 8-bit market leaders. PIC(Peripheral Interface Controller)

# Microcontroller

- The Atmel AVR series of microcontrollers has been popularized among hobbyists as the brain of the Arduino platform.

- Among 32-bit microcontrollers, Renesas leads the overall market, while ARM is a major player in mobile systems including the iPhone. Freescale, Samsung, Texas Instruments, and Infineon are other major microcontroller manufacturers.

- Focus on the PIC32MX675F512H, a member of Microchip's PIC32-series of microcontrollers based on the 32-bit MIPS microprocessor.

# Microcontrollers

- The PIC32 family also has a generous assortment of on-chip peripherals and memory

- □ Selected this family

- Inexpensive, easy-to-use development environment

- Based on the MIPS

- Microchip is a leading microcontroller vendor that sells more than a billion chips a year.

- Microcontroller I/O systems are quite similar from one manufacturer to another, so the principles illustrated on the PIC32 can readily be adapted to other microcontrollers.

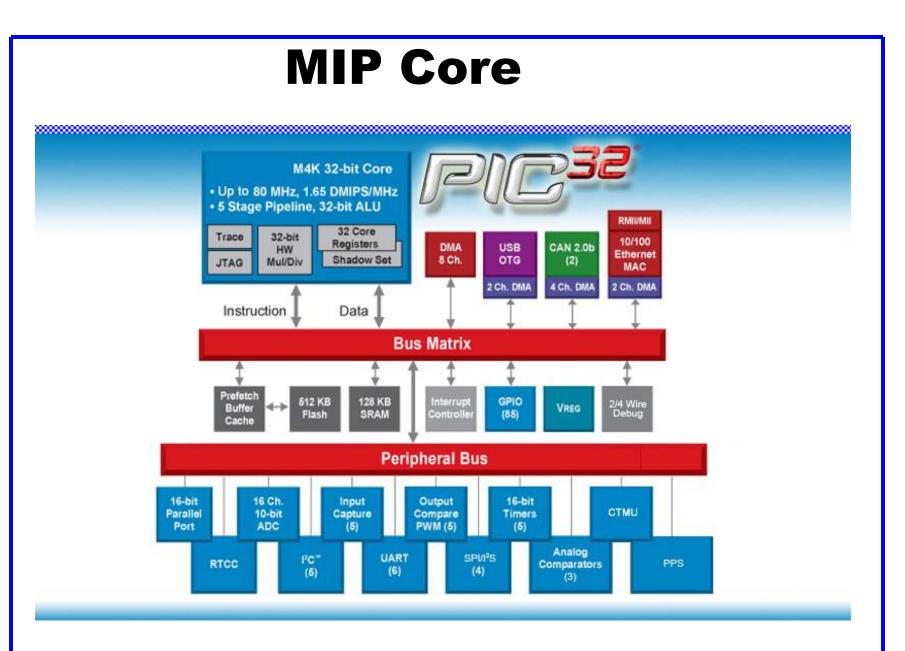

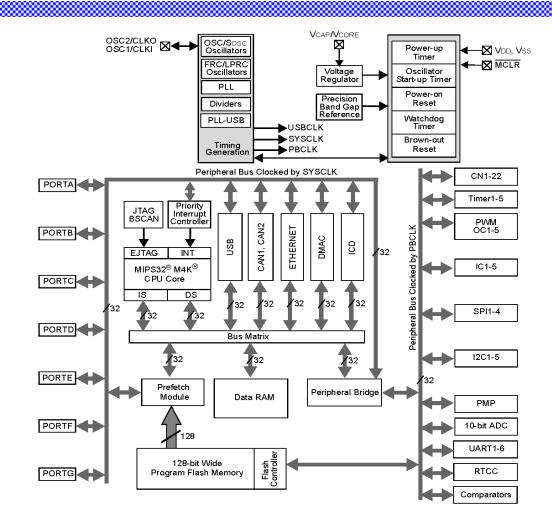

## PIC<sup>32</sup>(PIC32MX675F512H)

### □ MIPSM4K Core

- Up to 80 MHz, 1.65 DMIPS/MHz

- 5 Stage Pipeline devices

- Instruction Trace

- Temperature Range: -40°C to 105°C

- AEC-Q100 qualified

- Data and Code

- Up to 512 KB Flash (program code)

- Up to 64 KB SRAM (data)

- Prefetch Buffer 256KB Cache

- Separate Buses for Instructions and Data

### **PIC<sup>32</sup> Peripheral Interconnect**

Connected Peripherals with DMA

- Full-speed USB Host/Device/OTG

- 10/100 Ethernet MAC with MII/RMII Interfaces

- 2x CAN 2.0B Ports

- Up to 6 UART, 4 I<sup>2</sup>C<sup>™</sup>, 3 SPI Ports, CTMU and I S

- Up to 8 Additional Channels of General Purpose DMA

## **PIC<sup>32</sup> Peripheral Features**

| Parameter Name                           | Value                        |

|------------------------------------------|------------------------------|

| Family                                   | PIC32MX6xx                   |

| Max Speed MHz                            | 80                           |

| Program Memory Size (KB)                 | 512                          |

| RAM (KB)                                 | 64                           |

| Temperature Range (C)                    | -40 to 105                   |

| Operating Voltage Range (V)              | 2.3 to 3.6                   |

| DMA Channels                             | 8                            |

| SPI™                                     | 3                            |

| I <sup>2</sup> C <sup>™</sup> Compatible | 4                            |

| CTMU                                     | NO                           |

| USB (Channels, Speed, Compliance         | 1,FS Host/OTG,USB 2.0<br>OTG |

| A/D channels                             | 16                           |

| Max A/D Sample Rate (KSPS)               | 1000                         |

| Input Capture                            | 5                            |

| Output Compare/Std. PWM                  | 5                            |

| 16-bit Digital Timers                    | 5                            |

| Parallel Port                            | PMP                          |

| Comparators                              | 2                            |

| Internal Oscillator                      | 8 MHz, 32 kHz                |

| RTCC                                     | Yes                          |

| I/O Pins                                 | 53                           |

| Pin Count                                | 64                           |

### **PIC<sup>32</sup> Virtual Memory Map**

|                          | Virtual<br>Memory Map   | **** |

|--------------------------|-------------------------|------|

| 0xFFFFFFFF<br>0xBFC03000 | Reserved                |      |

| 0xBFC02FFF               | Device<br>Configuration |      |

| 0xBFC02FF0<br>0xBFC02FEF | Registers               |      |

| 0xBFC00000               | Boot Flash              |      |

| 0xBF900000               | Reserved                |      |

| 0xBF8FFFFF               | SFRs                    |      |

| 0xBF800000               | Reserved                |      |

| 0xBD080000<br>0xBD07FFFF | Reserved                |      |

| 0xBD000000               | Program Flash           |      |

| 0xA0020000               | Reserved                |      |

| 0xA001FFFF               | RAM                     |      |

| 0xA0000000               |                         |      |

## **PIC32** PinOut and Package

PIC32MX6xxFxxH pinout. Black pins are 5 V-tolerant EMDIO/AEMDIO/SCK3/U4TX/U1RTS/O0 ETXCLK/AERXERR/CN16/RD ERXCLK/EREFCLK/PMD3/RE AETXEN/ETXERR/CN15/RD6 \_3/SD03/U1TX/0C4/RD3 ERXDV/ECRSDV/PMD2/RE OC5/IC5/PMWR/CN13/RD4 SDA3/SDI3/U1RX/0C3/RD2 AETXD0/ERXD2/RF1 AETXD1/ERXD3/RF0 ERXERR/PMD4/RE4 ERXD1/PMD0/RE0 ERXD0/PMD1/RE1 PMRD/CN14/RD6 ICAP/NCORF 63 62 61 60 52 51 50 49 48 SOSCO/T1CK/CN0/RC14 ETXEN/PMD5/RE5 SOSCI/CN1/RC13 47 ETXD0/PMD6/RE6 46 OC1/INT0/RD0 ETXD1/PMD7/RE7 45 ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11 SCK2/U6TX/U3RTS/PMA5/CN8/RG6 ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10 SDA4/SDI2/U3RX/PMA4/CN9/RG7 44 AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9 43 SCL4/SDO2/U3TX/PMA3/CN10/RG8 PIC32MX664F064H RTCC/AERXD1/ETXD3/IC1/INT1/RD8 42 MCLR PIC32MX664F128H 41 🗌 Vss SS2/U6RX/U3CTS/PMA2/CN11/RG9 PIC32MX675F256H OSC2/CLKO/RC15 40 Vss q PIC32MX675F512H 39 OSC1/CLKI/RC12 VDD 10 PIC32MX695F512H 38 🗍 VDD AN5/C1IN+/VBUSON/CN7/RB5 11 D+/RG2 37 AN4/C1IN-/CN6/RB4 12 36 D-/RG3 AN3/C2IN+/CN5/RB3 13 35 VUSB AN2/C2IN-/CN4/RB2 14 34 VBUS PGEC1/AN1/VREF-/CVREF-/CN3/RB1 15 33 USBID/RF3 PGED1/AN0/VREF+/CVREF+/PMA6/CN2/RB0 16 PIC32 in 64-pin TQFP package 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 \_\_\_\_\_ AVSS TD0/AN10/CVREFOUT/PMA13/RB10 TD0/AN11/PMA12/RB11 V55 PGE C2/AN6/OCFA/RB6 ANB/SS4/U5RX/U2CTS/C10UT/RB8 AN9/C20UT/PMA7/RB9 AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15 SD45/SD14/U2RX/PMA9/CN17/RF4 SCL5/SD04/U2TX/PMA8/CN18/RF5 PGED2/AN7/RB AN14/SCK4/U5TX/U2RTS/PMALH/PMA1/RB1 TCK/AN12/PMA11/RB TDI/AN13/PMA10/RB IN GOD 200 YE TRUST

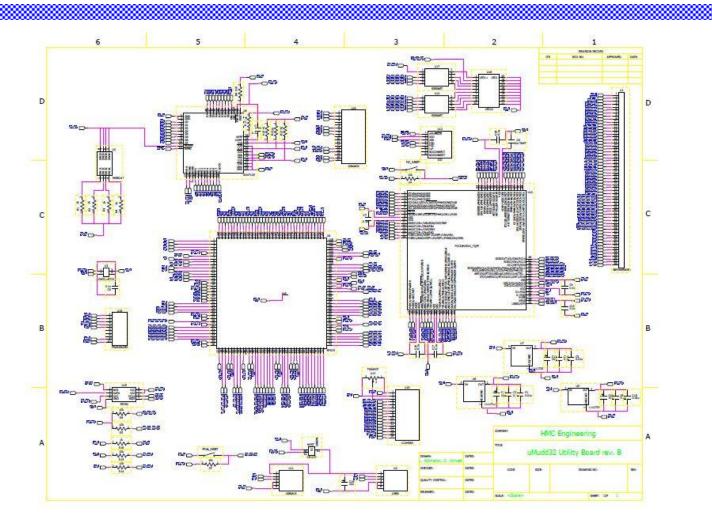

## uMudd32 Board

### schematic\_revB.tif

## **PIC Basic Operation**

14

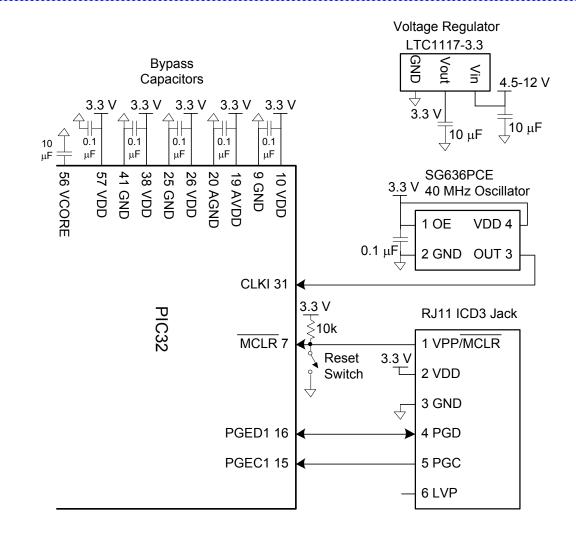

# **PIC Basic Operation**

#### Microchip ICD3

- Program the microcontroller is with a Microchip *In Circuit Debugger* (ICD) 3, or a puck.

- Communicate with the PIC32 from a PC to download code and to debug the program.

- Connects to a USB port on the PC and to a six-pin RJ-11 modular connector (US telephone jacks) on the PIC32 development board.

- The ICD3 communicates with the PIC over a 2-wire In-Circuit Serial Programming interface with a clock and a bidirectional data pin.

- Programming by using Microchip's free MPLAB Integrated Development Environment (IDE) to write your programs in assembly language or C, debug them in simulation, and download and test them on a development board by means of the ICD.

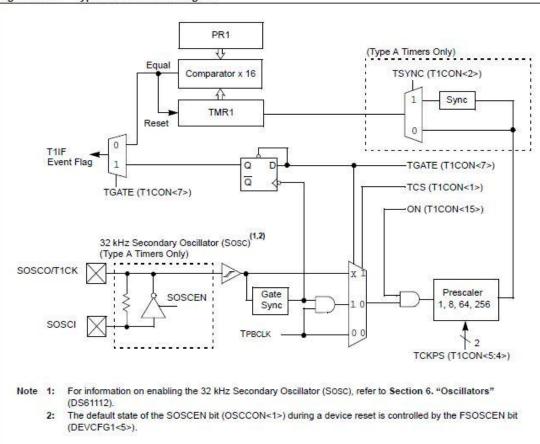

## Timers

$\Box$  5 timers:

- Timer1 (Type A)

- Timers 2/3, Timers4/5 (TypeB) 16-bit timer/counter

Common features:

- Software-selectable internal or external clock source

- Programmable interrupt generation and priority

- Gated external pulse counter

# Timers

### **I** Type A:

- Asynchronous timer/counter with a built-in oscillator

- Operational during CPU Sleep mode

- Software selectable prescalers 1:1, 1:8, 1:64 and 1:256

### Type B:

- Ability to form a 32-bit timer/counter

- Software prescalers 1:1, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64 and 1:256

- Event trigger capability

### **Type B Timer Block Diagram**

Figure 14-1: Type A Timer Block Diagram

# **Timer Registers**

| Table 14-2:              |              | s SFR Sumr        |                   | -                 |                   |                    |                   |                  |                  |

|--------------------------|--------------|-------------------|-------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| Name                     | Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| T1CON <sup>(3,4,5)</sup> | 31:24        |                   | -                 | -                 | -                 | -                  | -                 | —                | -                |

|                          | 23:16        | -                 | -                 | -                 | -                 | —                  | -                 | -                |                  |

|                          | 15:8         | ON                | FRZ               | SIDL              | TWDIS             | TWIP               | -                 | —                |                  |

|                          | 7:0          | TGATE             | -                 | TCKP              | S<1:0>            | -                  | TSYNC             | TCS              |                  |

| TxCON <sup>(3,4,5)</sup> | 31:24        |                   | -                 | -                 | -                 | -                  | -                 |                  |                  |

|                          | 23:16        | -                 | -                 | -                 | —                 |                    | . <del></del>     | —                |                  |

|                          | 15:8         | ON                | FRZ               | SIDL              | —                 | —                  | -                 | —                |                  |

|                          | 7:0          | TGATE             | TCKPS<2:0>(2)     |                   |                   | T32 <sup>(1)</sup> | -                 | TCS              |                  |

| TMRx <sup>(3,4,5)</sup>  | 31:24        |                   | -                 | -                 | -                 | -                  | -                 | -                | -                |

|                          | 23:16        | -                 | -                 | -                 | -                 | -                  | -                 | —                | -                |

|                          | 15:8         | TMRx<15:8>        |                   |                   |                   |                    |                   |                  |                  |

|                          | 7:0          | TMRx<7:0>         |                   |                   |                   |                    |                   |                  |                  |

| PRx <sup>(3,4,5)</sup>   | 31:24        | -                 | -                 | -                 | -                 | -                  | -                 | —                | -                |

|                          | 23:16        |                   | -                 | -                 | —                 |                    | -                 |                  |                  |

|                          | 15:8         | PRx<15:8>         |                   |                   |                   |                    |                   |                  |                  |

|                          | 7:0          |                   | PRx<7:0>          |                   |                   |                    |                   |                  |                  |

•TxCON: 16-bit control register associated with the timer

•TMRx: 16-bit timer count register

•PRx: 16-bit register associated with the timer

# **Timer1 Register**

| r-0               | r-0           | r-0            | r-0             | r-0          | r-0       | r-0            | r-0    |

|-------------------|---------------|----------------|-----------------|--------------|-----------|----------------|--------|

|                   |               |                | -               | —            | -         | -              | -      |

| bit 31            |               |                |                 |              |           | ta de de       | bit 24 |

| r-0               | r-0           | r-0            | r-0             | r-0          | r-0       | r-0            | r-0    |

| -                 | 1 1 <u></u> - |                | -               | -            | —         | -              |        |

| bit 23            |               |                |                 | 9<br>8-      |           | à à            | bit 16 |

| R/W-0             | R/W-0         | R/W-0          | R/W-0           | R-0          | r-0       | r-0            | r-0    |

| ON <sup>(1)</sup> | FRZ(2)        | SIDL           | TWDIS           | TWIP         | —         | _              | —      |

| bit 15            |               |                |                 |              | ••••••    | ta ,to         | bit 8  |

| R/W-0             | r-0           | R/W-0          | R/W-0           | r-0          | R/W-0     | R/W-0          | r-0    |

| TGATE             | -             | TCKPS<1:0>     |                 | —            | TSYNC     | TCS            | -      |

| bit 7             |               |                |                 |              | •         |                | bit 0  |

| Legend:           |               |                |                 |              |           |                |        |

| R = Readable b    | it            | W = Writable   | bit             | P = Program  | mable bit | r = Reserved I | bit    |

| U = Unimpleme     | nted bit      | -n = Bit Value | at POR: ('0' '1 | ' x = Unknov | (m)       |                |        |

### **Timer1 Control Registers**

- bit 31-16 **Reserved:** Write '0'; ignore read

- bit 15 **ON:** Timer On bit(1)

- 1 = Timer is enabled

- 0 = Timer is disabled

- bit 14 FRZ: Freeze in Debug Exception Mode bit(2)

- 1 = Freeze operation when CPU is in Debug Exception mode

- 0 = Continue operation even when CPU is in Debug Exception mode

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation even in Idle mode

- bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

- 1 = Writes to TMR1 are ignored until pending write operation completes

- 0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

- bit 11 **TWIP:** Asynchronous Timer Write in Progress bit

- In Asynchronous Timer mode:

- 1 = Asynchronous write to TMR1 register in progress

- 0 = Asynchronous write to TMR1 register complete

- In Synchronous Timer mode:

- This bit is read as '0'.

- bit 10-8 **Reserved:** Write '0'; ignore read

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit is writable only in Debug Exception mode. It is forced to '0' in normal mode.

### **Timer 1 Control Registers**

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit

- When TCS = 1:

- This bit is ignored and is read as '0'.

- When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 = Gated time accumulation is disabled

- bit 6 **Reserved:** Write '0'; ignore read

- □ bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

- 11 = 1:256 prescale value

- 10 = 1:64 prescale value

- 01 = 1:8 prescale value

- 00 = 1:1 prescale value

- bit 3 **Reserved:** Write '0'; ignore read

- bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit

- When TCS = 1:

- 1 = External clock input is synchronized

- 0 = External clock input is not synchronized

- When TCS = 0:

- This bit is ignored and is read as '0'.

- bit 1 TCS: Timer Clock Source Select bit

- 1 = External clock from TxCKI pin

- 0 = Internal peripheral clock

- bit 0 **Reserved:** Write '0'; ignore read

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit is writable only in Debug Exception mode. It is forced to '0' in normal mode.

## **Count to 1 sec**

TMRI prescale

Run periphery clock at  $\frac{1}{4}$  speed or 10MHz Pclk=clk/4 Prescale by 256 Each count (0.1us) x 256 = 25.6us Count =  $\frac{1 \, sec}{25.6 \, us}$  = 39062

# **Count to 1 sec**

### □ Start TMR1 at 0

□ Set T1CON

### □ Wait for TMRI=39062

```

la

$t1, TMR1

$zero, 0($t1) # reset timer1

SW

#T1CON:

# bit 15 = 1 On

#

14 = 1 FRZ (freeze on Debug exception)

#

5:4 = 11 Prescale by 256

ori $t1, $0, 16'b1100 0000 0011 0000

la $t0, T1CON

sw $t1 , 0($t0)

addi $t4, $0, 39062

la $t0, TMR1

poll:

lw $t3, 0($t0) # t3=TMR1

bne $t3, $t4, poll

nop

```