## E85 Digital Design & Computer Engineering

# Lecture 8: Arithmetic Circuits

### Lecture 8

- Chapter 5 Introduction

- Arithmetic Circuits

- 1-bit Adders

- N-bit Adders

- Ripple Adders

- Carry Lookahead Adders

- Prefix Adders

- Subtractors

- Arithmetic/Logic Units

### Chapter 5 Introduction

### Digital building blocks:

- Gates, multiplexers, decoders, registers, arithmetic circuits, counters, memory arrays, logic arrays

- Building blocks demonstrate hierarchy, modularity, and regularity:

- Hierarchy of simpler components

- Well-defined interfaces and functions

- Regular structure easily extends to different sizes

- Will use these building blocks in Chapter

7 to build microprocessor

## 1-Bit Adders

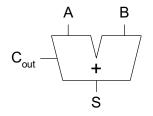

Half Adder

| Α | В | C <sub>out</sub> | S |

|---|---|------------------|---|

| 0 | 0 | -                | = |

| 0 | 1 |                  |   |

| 1 | 0 |                  |   |

| 1 | 1 |                  |   |

$$S = C_{out} = 0$$

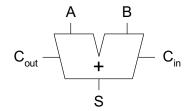

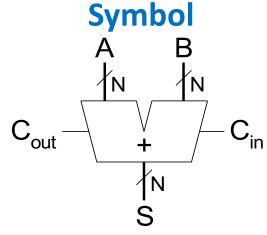

## Full Adder

| $C_{in}$ | Α | В | C <sub>out</sub> | S |

|----------|---|---|------------------|---|

| 0        | 0 | 0 |                  |   |

| 0        | 0 | 1 |                  |   |

| 0        | 1 | 0 |                  |   |

| 0        | 1 | 1 |                  |   |

| 1        | 0 | 0 |                  |   |

| 1        | 0 | 1 |                  |   |

| 1        | 1 | 0 |                  |   |

| 1        | 1 | 1 |                  |   |

### Multibit Adders (CPAs)

Types of carry propagate adders (CPAs):

Ripple-carry (slow)

Carry-lookahead (fast)

Prefix (faster)

Carry-lookahead and prefix adders faster for large adders but require more hardware

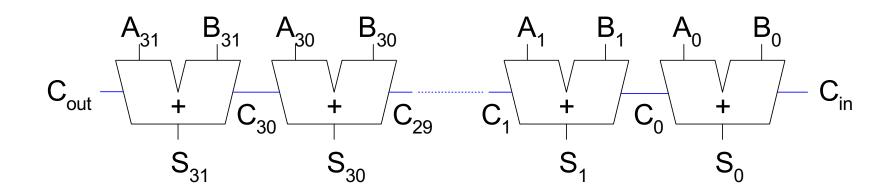

## Ripple-Carry Adder

- Chain 1-bit adders together

- Carry ripples through entire chain

- Disadvantage: slow

## Ripple-Carry Adder Delay

$$t_{\text{ripple}} = Nt_{FA}$$

where  $t_{FA}$  is the delay of a 1-bit full adder

### Carry-Lookahead Adder

#### Compute C<sub>out</sub> for k-bit blocks using generate and propagate signals

#### Some definitions:

- Column i produces a carry out by either generating a carry out or propagating a carry in to the carry out

- Generate  $(G_i)$  and propagate  $(P_i)$  signals for each column:

- **Generate:** Column *i* will generate a carry out if  $A_i$  and  $B_i$  are both 1.

$$G_i =$$

• **Propagate:** Column *i* will propagate a carry in to the carry out if  $A_i$  or  $B_i$  is 1.

$$P_i = 1$$

• Carry out: The carry out of column *i* (*C<sub>i</sub>*) is:

$$C_i =$$

### Block Propagate and Generate

Now use column Propagate and Generate signals to compute *Block Propagate* and *Generate* signals for k-bit blocks, i.e.:

- Compute if a k-bit group will propagate a carry in (to the block)

to the carry out (of the block)

- Compute if a k-bit group will generate a carry out (of the block)

### Block Propagate and Generate Signals

• **Example:** Block propagate and generate signals for 4-bit blocks ( $P_{3:0}$  and  $G_{3:0}$ ):

$$P_{3:0} = P_3 P_2 P_1 P_0$$

$$G_{3:0} = G_3 + G_2 P_3 + G_1 P_2 P_3 + G_0 P_1 P_2 P_3$$

$$= G_3 + P_3 (G_2 + P_2 (G_1 + P_1 G_0))$$

### Block Propagate and Generate Signals

In general for a block spanning bits i through j,

$$P_{i:j} = P_{i}P_{i-1}P_{i-2...}P_{j}$$

$$G_{i:j} = G_{i} + P_{i}(G_{i-1} + P_{i-1}(G_{i-2} + P_{i-2...}G_{j}))$$

$$C_{i} = G_{i:j} + P_{i:j}C_{j-1}$$

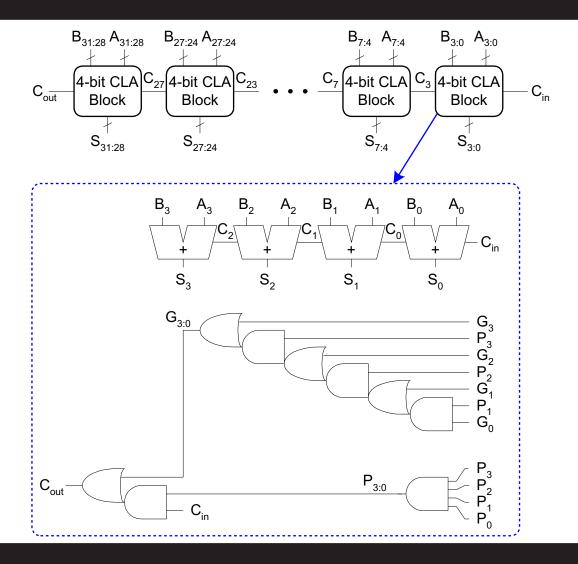

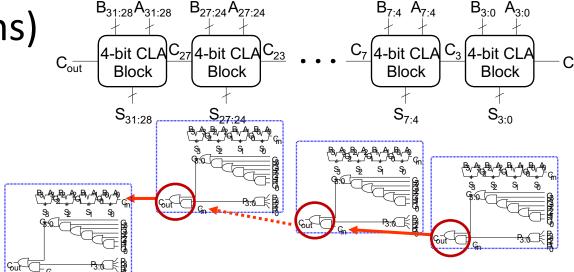

### 32-bit CLA with 4-bit Blocks

- Step 1: Compute  $G_i$  and  $P_i$  for all columns

- Step 2: Compute G and P for k-bit blocks

- Step 3:  $C_{in}$  propagates through each k-bit propagate/generate logic (meanwhile computing sums)

- Step 4: Compute sum for most significant kbit block

• Step 1: Compute  $G_i$  and  $P_i$  for all columns

$$G_i = A_i B_i$$

$$P_i = A_i + B_i$$

- Step 1: Compute  $G_i$  and  $P_i$  for all columns

- Step 2: Compute G and P for k-bit blocks

$$P_{3:0} = P_3 P_2 P_1 P_0$$

$$G_{3:0} = G_3 + P_3 (G_2 + P_2 (G_1 + P_1 G_0))$$

- Step 1: Compute  $G_i$  and  $P_i$  for all columns

- Step 2: Compute G and P for k-bit blocks

- Step 3:  $C_{in}$  propagates through each k-bit propagate/generate logic (meanwhile

computing sums)

- Step 1: Compute  $G_i$  and  $P_i$  for all columns

- Step 2: Compute G and P for k-bit blocks

- **Step 3:**  $C_{in}$  propagates through each k-bit propagate/generate logic (meanwhile computing sums)

- Step 4: Compute sum for most significant k-

bit block

## Carry-Lookahead Adder Delay

For *N*-bit CLA with *k*-bit blocks:

$$t_{CLA} = t_{pg} + t_{pg\_block} + (N/k - 1)t_{AND\_OR} + kt_{FA}$$

$-t_{pg}$ : delay to generate all  $P_i$ ,  $G_i$

$-t_{pg\ block}$ : delay to generate all  $P_{i:j}, G_{i:j}$

-  $t_{

m AND~OR}$ : delay from  $C_{

m in}$  to  $C_{

m out}$  of final AND/OR gate in k-bit CLA block

An N-bit carry-lookahead adder is generally much faster than a ripple-carry adder for N > 16

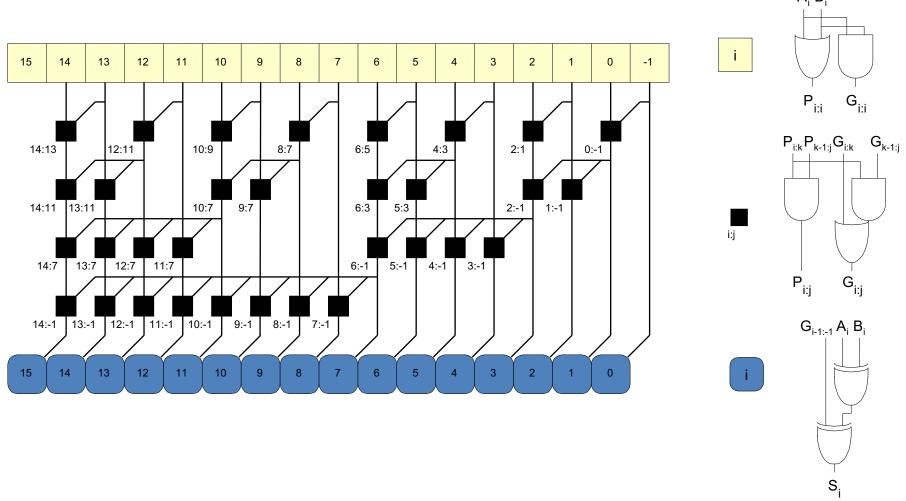

### Prefix Adder

• Computes carry in  $(C_{i-1})$  for each column, then computes sum:

$$S_i = (A_i \wedge B_i) \wedge C_{i-1}$$

- Computes G and P for 1-, 2-, 4-, 8-bit blocks, etc.

until all G<sub>i</sub> (carry in) known

- log<sub>2</sub>N stages

### Prefix Adder

- Carry in either generated in a column or propagated from a previous column.

- Column -1 holds  $C_{in}$ , so

$$G_{-1} = C_{\text{in}}$$

• Carry in to column *i* = carry out of column *i*-1:

$$C_{i-1} = G_{i-1:-1}$$

$G_{i-1:-1}$ : generate signal spanning columns i-1 to -1

Sum equation:

$$S_i = (A_i \wedge B_i) \wedge G_{i-1:-1}$$

• **Goal:** Quickly compute  $G_{0:-1}$ ,  $G_{1:-1}$ ,  $G_{2:-1}$ ,  $G_{3:-1}$ ,  $G_{4:-1}$ ,  $G_{5:-1}$ , ... (called *prefixes*) (=  $C_0$ ,  $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_4$ ,  $C_5$ , ...)

### Prefix Adder

Generate and propagate signals for a block spanning bits i:j

$$G_{i:j} = G_{i:k} + P_{i:k} G_{k-1:j}$$

$$P_{i:j} = P_{i:k}P_{k-1:j}$$

- In words:

- Generate: block i:j will generate a carry if:

- upper part (i:k) generates a carry or

- upper part (i:k) propagates a carry generated in lower part (k-1:j)

- Propagate: block i:j will propagate a carry if both the upper and lower parts propagate the carry

### 16-Bit Prefix Adder Schematic

### Prefix Adder Delay

$$t_{PA} = t_{pg} + \log_2 N(t_{pg\_prefix}) + t_{XOR}$$

$t_{pg}$ : delay to produce  $P_i$ ,  $G_i$  (AND or OR gate)

$t_{pg}$  prefix: delay of black prefix cell (AND-OR gate)

### Adder Delay Comparisons

#### Compare delay of: 32-bit ripple-carry, CLA, and prefix adders

- CLA has 4-bit blocks

- 2-input gate delay = 10 ps; full adder delay = 30 ps

$$t_{ripple} = Nt_{FA} = 32(30 \text{ ps})$$

$= 960 \text{ ps}$

$t_{CLA} = t_{pg} + t_{pg\_block} + (N/k - 1)t_{AND\_OR} + kt_{FA}$

$= [10 + 60 + (7)20 + 4(30)] \text{ ps}$

$= 330 \text{ ps}$

$t_{PA} = t_{pg} + \log_2 N(t_{pg\_prefix}) + t_{XOR}$

$= [10 + \log_2 32(20) + 10] \text{ ps}$

$= 120 \text{ ps}$

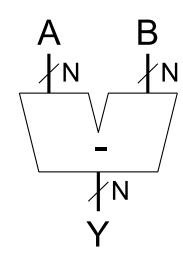

### Subtracter

### **Symbol**

### **Implementation**

A E

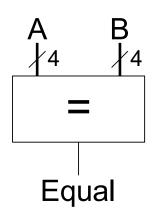

## Comparator: Equality

#### **Symbol**

#### **Implementation**

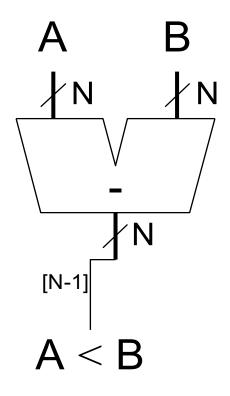

### Comparator: Less Than

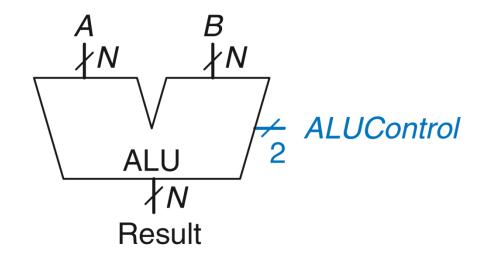

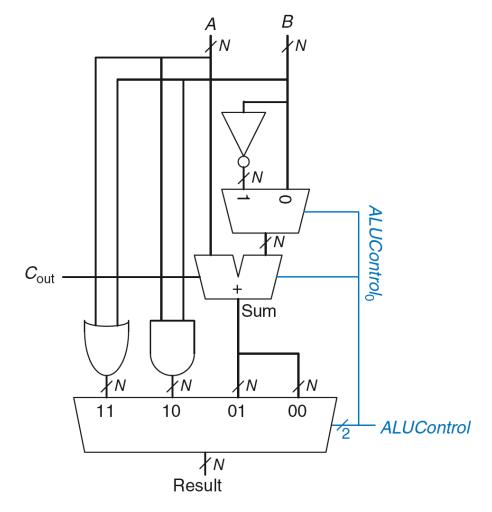

### **ALU** should perform:

- Addition

- Subtraction

- AND

- OR

| ALUControl <sub>1:0</sub> | Function |

|---------------------------|----------|

| 00                        | Add      |

| 01                        | Subtract |

| 10                        | AND      |

| 11                        | OR       |

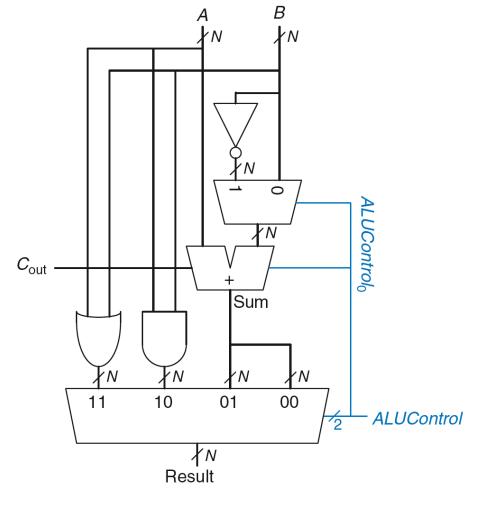

### Example: Perform A + B

$$ALUControl = 00$$

$$Result = A + B$$

| ALUControl <sub>1:0</sub> | Function |

|---------------------------|----------|

| 00                        | Add      |

| 01                        | Subtract |

| 10                        | AND      |

| 11                        | OR       |

**Example:** Perform A OR B

| ALUControl <sub>1:0</sub> | Function |

|---------------------------|----------|

| 00                        | Add      |

| 01                        | Subtract |

| 10                        | AND      |

| 11                        | OR       |

#### **Example:** Perform A OR B

$ALUControl_{1:0} = 11$

Mux selects output of OR gate as Result, so

Result = A OR B

| ALUControl <sub>1:0</sub> | Function |

|---------------------------|----------|

| 00                        | Add      |

| 01                        | Subtract |

| 10                        | AND      |

| 11                        | OR       |

**Example:** Perform A + B

| ALUControl <sub>1:0</sub> | Function |

|---------------------------|----------|

| 00                        | Add      |

| 01                        | Subtract |

| 10                        | AND      |

| 11                        | OR       |

#### **Example:** Perform A + B

$ALUControl_{1:0} = 00$

$ALUControl_0 = 0$ , so:

$C_{in}$  to adder = 0

2<sup>nd</sup> input to adder is B

Mux selects Sum as Result, so

Result = A + B

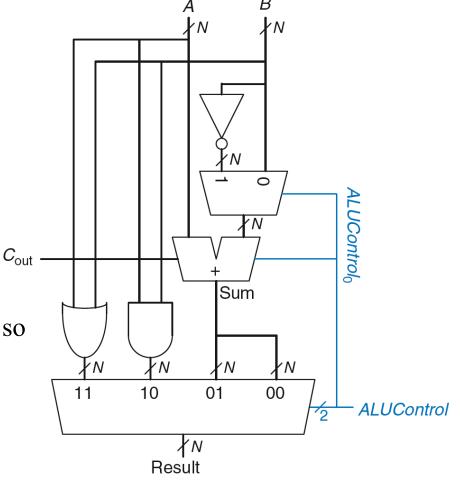

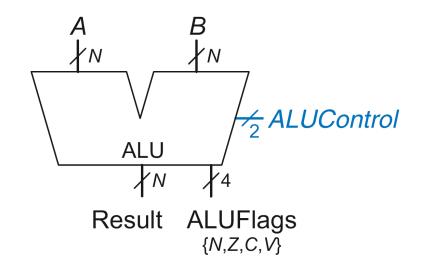

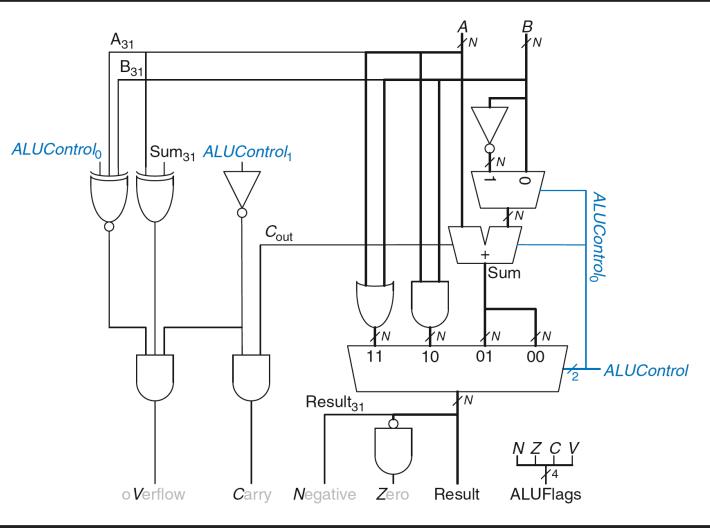

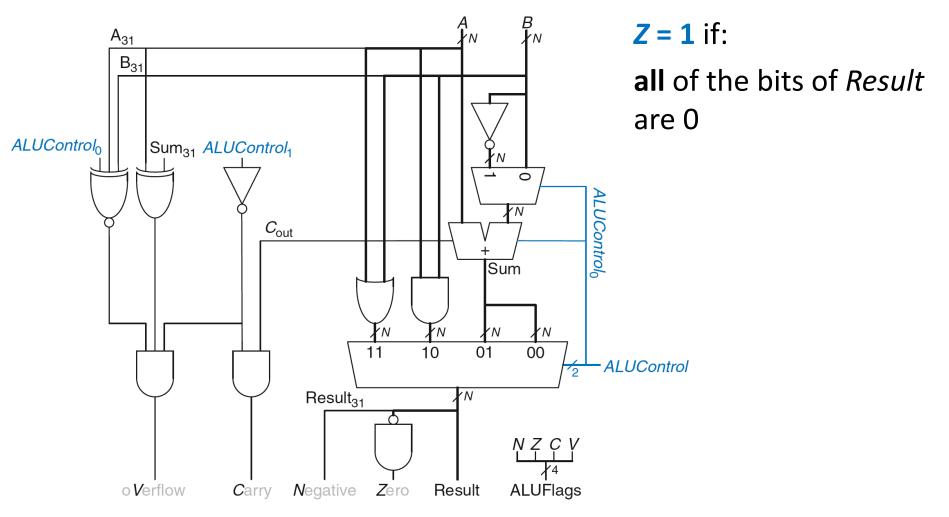

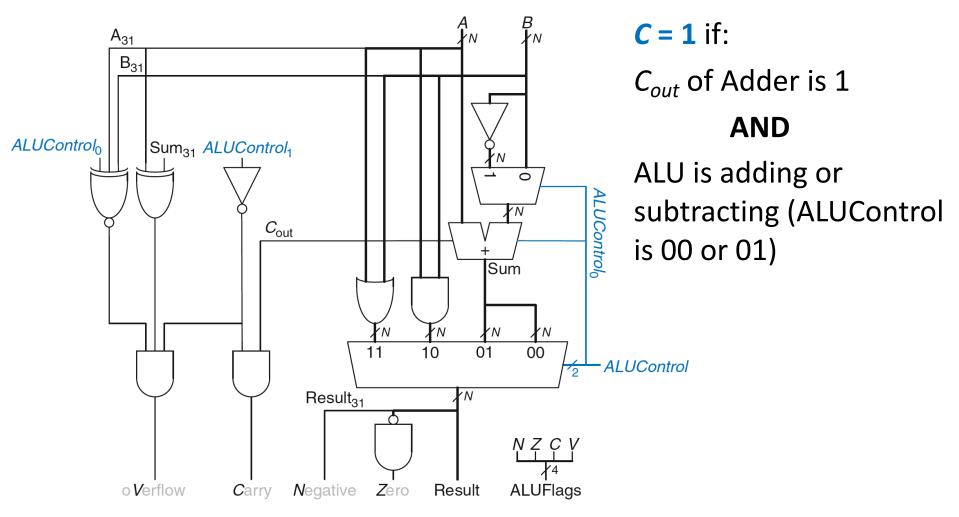

## **ALU** with Status Flags

| Flag | Description              |

|------|--------------------------|

| N    | Result is Negative       |

| Z    | Result is Zero           |

| С    | Adder produces Carry out |

| V    | Adder oVerflowed         |

## **ALU with Status Flags**

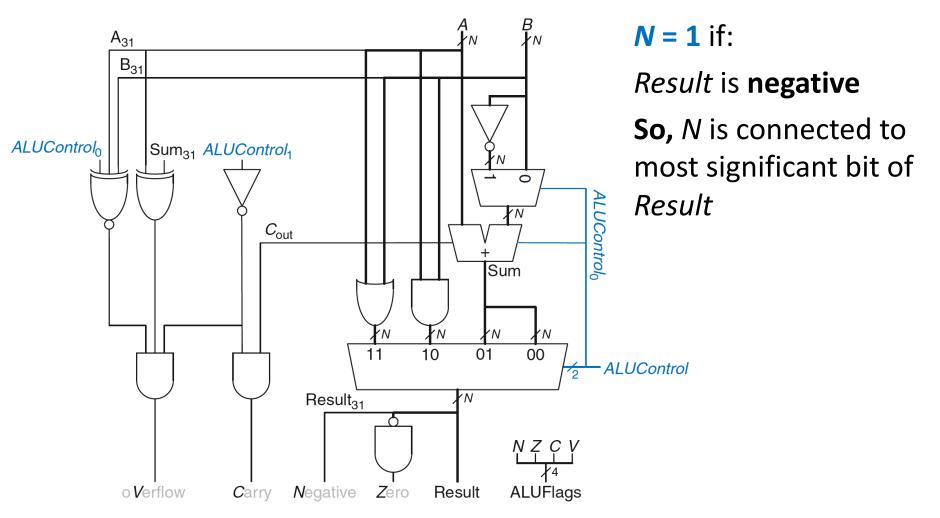

### ALU with Status Flags: Negative

### ALU with Status Flags: Zero

### ALU with Status Flags: Carry

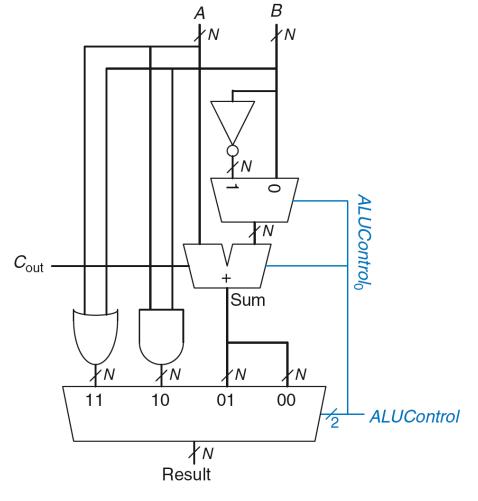

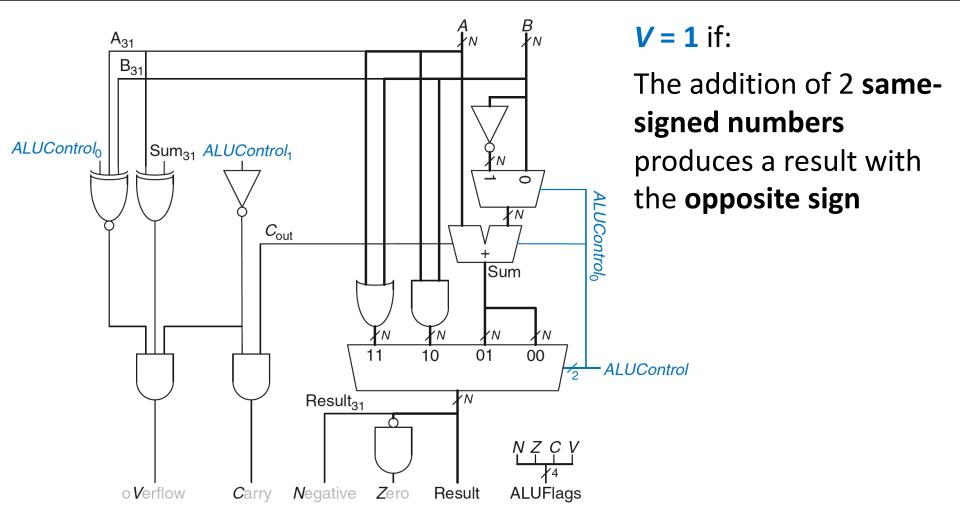

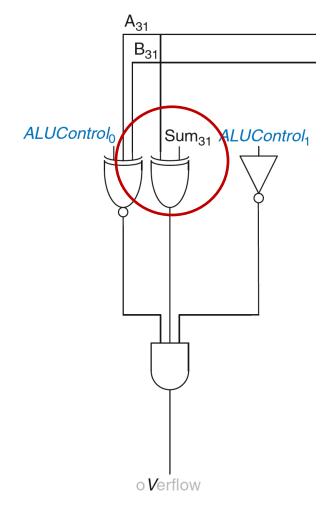

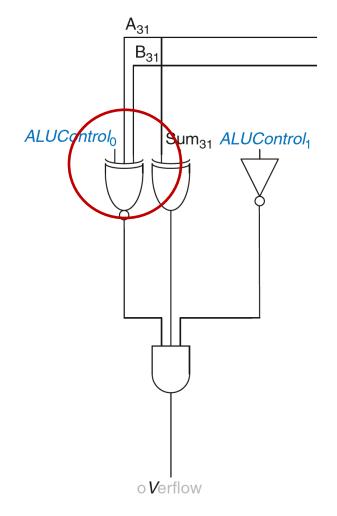

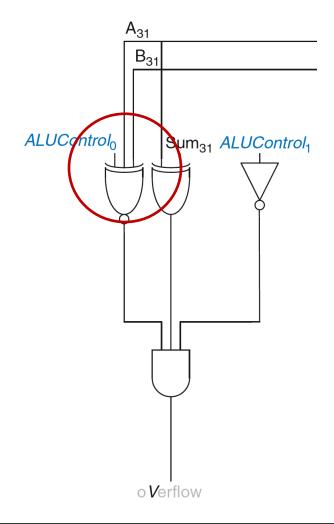

$$V = 1$$

if:

ALU is performing addition or subtraction  $(ALUControl_1 = 0)$

$$V = 1$$

if:

ALU is performing addition or subtraction  $(ALUControl_1 = 0)$

#### **AND**

A and Sum have opposite signs

$$V = 1$$

if:

ALU is performing addition or subtraction  $(ALUControl_1 = 0)$

#### **AND**

A and Sum have opposite signs

#### **AND**

A and B have same signs upon addition **OR**

A and B have different signs upon subtraction

$$V = 1$$

if:

ALU is performing addition or subtraction  $(ALUControl_1 = 0)$

#### **AND**

A and Sum have opposite signs

#### **AND**

A and B have same signs upon addition  $(ALUControl_0 = 0)$  OR

A and B have different signs upon subtraction  $(ALUControl_0 = 1)$