## E85: Digital Design and Computer Engineering Problem Set 3

1) Suppose propagation delays for a 10-nm integrated circuit process are given in the table below.

| Cell  | Propagation Delay (ps) | Contamination Delay (ps) |

|-------|------------------------|--------------------------|

| NOT   | 6                      | 4                        |

| NAND2 | 8                      | 6                        |

| NOR2  | 10                     | 8                        |

| NAND3 | 10                     | 8                        |

| NOR3  | 12                     | 10                       |

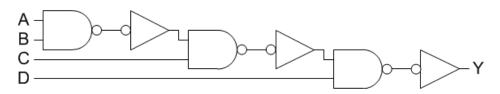

Determine the propagation and contamination delays of the following circuit. Redesign it to accomplish the same function while minimizing propagation delay, using only gates from the table above. What are the propagation and contamination delays of your optimized circuit?

2) Latches and Flip-Flops

Do Exercises 3.4 and 3.6 from the textbook.

3) Combinational and Sequential Logic

Do Exercise 3.18 from the textbook.

4) FSM design

Do Exercise 3.26 from the textbook. Just sketch the state transition diagram. Don't do the schematic that is requested in the problem. *Extra Credit*: Finish the schematic. Don't start on the extra credit until you've finished the rest of PS 3. You do have other classes, and all humans need sleep.

5) Impact on society: Name a system (other than a traffic light or soda machine dispenser) that you encounter in daily life that is readily described as a finite state machine.

How long did you spend on this problem set? This will not count toward your grade but will help calibrate the workload.