# E85: Digital Design and Computer Engineering Problem Set 2

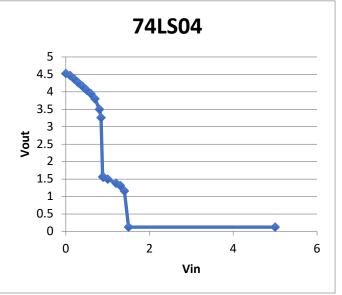

1) The voltage transfer characteristics below are measured for a 74LS04 operating at 5V. Determine VIL, VIH, VOL, VOH, and the high and low noise margins. Compare your results to the 74LS specification in Table eA.2 of the textbook. Are they within the specifications?

- 2) Referring to the logic level specifications in Tables eA.2 and eA.3 of the textbook:

- a) What could go wrong if a 74LS04 inverter drives a 74HC08 AND gate?

- b) In light of your answer to Part (a), why does the HCT family exist?

- c) i) Can a 3.3V 74LVC32 gate reliably drive a 5V 74HC00?

- ii) Can a 3.3V 74LVC32 gate reliably drive a 5V 74HCT00?

- iii) Can a 74HC00 reliably drive a 3.3V 74LVC32?

- 3) Power consumption

Hint: refer to the Switches and Diodes Tutorial at the end of this problem set if you are unfamiliar with electrical calculations for these components.

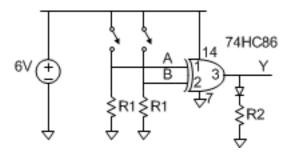

The following circuit turns on an LED when you press one button or another but not both. The circuit operates directly from a 6V Ni-MH battery with a 280 mA-hr energy capacity. The data sheet for the 74HC86 XOR gate is attached to the end of this problem set. The circuit is in a hot enclosure that might reach 85 °C. You push the buttons slowly enough that dynamic power consumption is negligible.

- a) What is the quiescent power consumption of the XOR gate in the hot enclosure?

- b) What value of R1 should you use to minimize power consumption when the button is pressed, while still providing a valid logic level at the input of the XOR when the button is not pressed, considering input leakage current?

- c) What value of R2 should you use to maximize the brightness of the LED without exceeding the IOH output current specification? Assume that the LED has a 2 V drop across it when ON.

- d) Suppose that both buttons are pressed 99.9% of the time and that a single button is pressed the remainder of the time. What is the average power consumption? Be sure to account for quiescent consumption of the gate, power dissipated in the input resistors, and power delivered to the load.

- e) How long will the battery last?

- f) If you were willing to violate IOH, what is the minimum value of R2 that you could use without risking damage to the 74HC86?

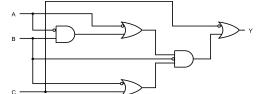

- 4) Consider the following logic circuit:

- a) Write the Boolean equation performed by the above diagram.

- b) Simplify the equation using Boolean identities.

- c) Write a truth table describing the circuit.

- d) Show how to implement the simplified function with logic gates.

- e) Show how to implement the function in SystemVerilog.

- f) Sketch a transistor-level implementation of the simplified function using CMOS transistors.

- 5) Impact on Society: Integrated circuits have been following Moore's Law since 1965, with cost per transistor reducing approximately 30% per year. This progress is slowing as nanometer lithography is becoming extremely expensive. Supposing cost reduction grinds to a halt by 2022, write a thoughtful paragraph predicting a significant impact on society caused by the end of Moore's Law.

How long did you spend on this problem set? This will not count toward your grade but will help calibrate the workload.

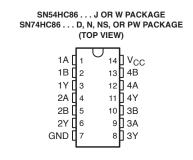

### SN54HC86, SN74HC86 QUADRUPLE 2-INPUT EXCLUSIVE-OR GATES

±4-mA Output Drive at 5 V

True Logic

Low Input Current of 1 µA Max

SCLS100E - DECEMBER 1982 - REVISED AUGUST 2003

- Wide Operating Voltage Range of 2 V to 6 V

- Outputs Can Drive Up To 10 LSTTL Loads

- Low Power Consumption, 20-µA Max I<sub>CC</sub>

- Typical t<sub>pd</sub> = 10 ns

NC - No internal connection

#### description/ordering information

These devices contain four independent 2-input exclusive-OR gates. They perform the Boolean function  $Y = A \oplus B$  or  $Y = \overline{AB} + A\overline{B}$  in positive logic.

•

A common application is as a true/complement element. If one of the inputs is low, the other input is reproduced in true form at the output. If one of the inputs is high, the signal on the other input is reproduced inverted at the output.

| TA             | PACKA      | GET          | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |  |  |  |  |  |

|----------------|------------|--------------|--------------------------|---------------------|--|--|--|--|--|

|                | PDIP – N   | Tube of 25   | SN74HC86N                | SN74HC86N           |  |  |  |  |  |

|                |            | Tube of 50   | SN74HC86D                |                     |  |  |  |  |  |

|                | SOIC – D   | Reel of 2500 | SN74HC86DR               | HC86                |  |  |  |  |  |

| –40°C to 85°C  |            | Reel of 250  | SN74HC86DT               |                     |  |  |  |  |  |

|                | SOP – NS   | Reel of 2000 | SN74HC86NSR              | HC86                |  |  |  |  |  |

|                |            | Tube of 90   | SN74HC86PW               |                     |  |  |  |  |  |

|                | TSSOP – PW | Reel of 2000 | SN74HC86PWR              | HC86                |  |  |  |  |  |

|                |            | Reel of 250  | SN74HC86PWT              |                     |  |  |  |  |  |

|                | CDIP – J   | Tube of 25   | SNJ54HC86J               | SNJ54HC86J          |  |  |  |  |  |

| –55°C to 125°C | CFP – W    | Tube of 150  | SNJ54HC86W               | SNJ54HC86W          |  |  |  |  |  |

|                | LCCC – FK  | Tube of 55   | SNJ54HC86FK              | SNJ54HC86FK         |  |  |  |  |  |

#### **ORDERING INFORMATION**

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2003, Texas Instruments Incorporated On products compliant to MIL-PRF-38535, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters.

#### SN54HC86, SN74HC86 QUADRUPLE 2-INPUT EXCLUSIVE-OR GATES

SCLS100E - DECEMBER 1982 - REVISED AUGUST 2003

|   | FUNCTION TABLE<br>(each gate) |     |        |  |  |  |  |  |  |

|---|-------------------------------|-----|--------|--|--|--|--|--|--|

| Γ | INP                           | UTS | OUTPUT |  |  |  |  |  |  |

| Γ | Α                             | В   | Y      |  |  |  |  |  |  |

| Γ | L                             | L   | L      |  |  |  |  |  |  |

| L | L                             | н   | н      |  |  |  |  |  |  |

|   | Н                             | L   | н      |  |  |  |  |  |  |

|   | н                             | Н   | L      |  |  |  |  |  |  |

#### exclusive-OR logic

An exclusive-OR gate has many applications, some of which can be represented better by alternative logic symbols.

These are five equivalent exclusive-OR symbols valid for an 'HC86 gate in positive logic; negation may be shown at any two ports.

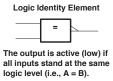

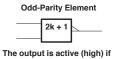

Even-Parity Element

2k

The output is active (low) if an even number of inputs (i.e., 0 or 2) are active.

an odd number of inputs (i.e., only 1 of the 2) are active.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub>                                                               |                |   |

|-----------------------------------------------------------------------------------------------------|----------------|---|

| Input clamp current, $I_{IK}$ (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>CC</sub> ) (see Note 1 | 1) ±20 mA      |   |

| Output clamp current, $I_{OK}$ (V <sub>O</sub> < 0 or V <sub>O</sub> > V <sub>CC</sub> ) (see N     | lote 1) ±20 mA |   |

| Continuous output current, $I_{O}$ (V <sub>O</sub> = 0 to V <sub>CC</sub> )                         |                |   |

| Continuous current through V <sub>CC</sub> or GND                                                   | ±50 mA         |   |

| Package thermal impedance, $\theta_{IA}$ (see Note 2): D packa                                      | age            | ! |

| N packa                                                                                             | age            | 1 |

| NS pack                                                                                             | ckage          | ! |

| PW pac                                                                                              | ckage 113°C/W  | ! |

| Storage temperature range, T <sub>stg</sub>                                                         | •              |   |

|                                                                                                     |                |   |

<sup>+</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed. 2. The package thermal impedance is calculated in accordance with JESD 51-7.

## SN54HC86, SN74HC86 QUADRUPLE 2-INPUT EXCLUSIVE-OR GATES

SCLS100E - DECEMBER 1982 - REVISED AUGUST 2003

3

#### recommended operating conditions (see Note 3)

|                              |                                 |                         | s    | SN54HC86 SN74HC |      |      |     | 36   | UNIT |

|------------------------------|---------------------------------|-------------------------|------|-----------------|------|------|-----|------|------|

|                              |                                 |                         | MIN  | NOM             | MAX  | MIN  | NOM | MAX  | UNII |

| VCC                          | Supply voltage                  |                         | 2    | 5               | 6    | 2    | 5   | 6    | V    |

| VIH High-level input voltage |                                 | V <sub>CC</sub> = 2 V   | 1.5  |                 |      | 1.5  |     |      | v    |

|                              | High-level input voltage        | V <sub>CC</sub> = 4.5 V | 3.15 |                 |      | 3.15 |     |      |      |

|                              |                                 | V <sub>CC</sub> = 6 V   | 4.2  |                 |      | 4.2  |     |      |      |

|                              |                                 | V <sub>CC</sub> = 2 V   |      |                 | 0.5  |      |     | 0.5  | V    |

| V <sub>IL</sub> Low-lev      | Low-level input voltage         | V <sub>CC</sub> = 4.5 V |      |                 | 1.35 |      |     | 1.35 |      |

|                              |                                 | V <sub>CC</sub> = 6 V   |      |                 | 1.8  |      |     | 1.8  |      |

| VI                           | Input voltage                   |                         | 0    |                 | VCC  | 0    |     | VCC  | V    |

| VO                           | Output voltage                  |                         | 0    |                 | VCC  | 0    |     | VCC  | V    |

| ∆t/∆v Inp                    | Input transition rise/fall time | V <sub>CC</sub> = 2 V   |      |                 | 1000 |      |     | 1000 |      |

|                              |                                 | V <sub>CC</sub> = 4.5 V |      |                 | 500  |      |     | 500  | ns   |

|                              |                                 | V <sub>CC</sub> = 6 V   |      |                 | 400  |      |     | 400  |      |

| Тд                           | Operating free-air temperature  |                         | -55  |                 | 125  | -40  |     | 85   | °C   |

NOTE 3: All unused inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER | TEST CONDITIONS                   |                           | vcc ·      | T <sub>A</sub> = 25°C |       | SN54HC86 |     | SN74HC86 |      | UNIT  |      |

|-----------|-----------------------------------|---------------------------|------------|-----------------------|-------|----------|-----|----------|------|-------|------|

| PARAMETER |                                   |                           |            | MIN                   | TYP   | MAX      | MIN | MAX      | MIN  | MAX   | UNIT |

|           |                                   |                           | 2 V        | 1.9                   | 1.998 |          | 1.9 |          | 1.9  |       |      |

|           |                                   | I <sub>OH</sub> = -20 μA  | 4.5 V      | 4.4                   | 4.499 |          | 4.4 |          | 4.4  |       | v    |

| VOH       | $V_I = V_{IH} \text{ or } V_{IL}$ |                           | 6 V        | 5.9                   | 5.999 |          | 5.9 |          | 5.9  |       |      |

|           |                                   | $I_{OH} = -4 \text{ mA}$  | 4.5 V      | 3.98                  | 4.3   |          | 3.7 |          | 3.84 |       |      |

|           |                                   | I <sub>OH</sub> = -5.2 mA | 6 V        | 5.48                  | 5.8   |          | 5.2 |          | 5.34 |       |      |

| VOL       | $V_I = V_{IH} \text{ or } V_{IL}$ |                           | 2 V        |                       | 0.002 | 0.1      |     | 0.1      |      | 0.1   | v    |

|           |                                   | I <sub>OL</sub> = 20 μA   | 4.5 V      |                       | 0.001 | 0.1      |     | 0.1      |      | 0.1   |      |

|           |                                   |                           | 6 V        |                       | 0.001 | 0.1      |     | 0.1      |      | 0.1   |      |

|           |                                   | $I_{OL} = 4 \text{ mA}$   | 4.5 V      |                       | 0.17  | 0.26     |     | 0.4      |      | 0.33  |      |

|           |                                   | I <sub>OL</sub> = 5.2 mA  | 6 V        |                       | 0.15  | 0.26     |     | 0.4      |      | 0.33  |      |

| Ц         | $V_I = V_{CC} \text{ or } 0$      |                           | 6 V        |                       | ±0.1  | ±100     |     | ±1000    |      | ±1000 | nA   |

| ICC       | $V_I = V_{CC} \text{ or } 0,$     | I <sub>O</sub> = 0        | 6 V        |                       |       | 2        |     | 40       |      | 20    | μA   |

| Ci        |                                   |                           | 2 V to 6 V |                       | 3     | 10       |     | 10       |      | 10    | pF   |

# **Switches and Diodes Tutorial**

A single-pole single-throw (SPST) switch or button is either open or closed, blocking or allowing current to flow, respectively. To produce a digital logic level, the switch is normally placed in series with a resistor, as shown below.

(a) Switch with pulldown resistor

$$\stackrel{\land}{\downarrow}$$

(b) LED with current-limiting resistor  $\overset{\mathsf{R}}{\downarrow}$

Assume that the switch has negligible internal resistance. When the switch is closed, the output Y is pulled up to V<sub>DD</sub> through the switch. The circuit dissipates  $P = V_{DD}^2/R$  across the resistor. When the switch is open, the output Y is pulled down close to 0 through the resistor. If the load draws some current  $I_{load}$  (e.g. the input leakage current of a gate attached to Y), it will cause a voltage drop  $V_Y = I_{load} * R$  across the resistor instead of getting all the way down to 0.

The resistor should be chosen according to the Goldilocks principle: not too big, not too small, but just right. If the resistor is too large,  $V_Y$  won't fall low enough. If the resistor is too small, the circuit dissipates excessive and wasteful power (or might even melt down). As a practical matter, this often means the resistor is selected in the 1-10 K $\Omega$  range such that the power is small and leakage causes a negligible disturbance to the output voltage. However, if extremely low power operation is needed, a larger resistor would be appropriate and the leakage must be considered more carefully so that the output voltage remains a valid low logic level.

A light emitting diode (LED) can be approximated as OFF when the voltage across the diode is less than some voltage  $V_D$  and ON when the voltage is greater than  $V_D$ . VD varies from about 1.7 to 2.3 V depending on the color of the diode and the ambient temperature, but 2.0 V is a reasonable average for rough calculations. When the diode is off, it draws negligible current. When it is ON, it draws as much current  $I_D$  as it can, and the brightness is proportional to the current. However, if the current is too great, the diode or the device sourcing the current will burn out. Hence, diodes are normally used with current-limiting resistors, as shown above. Ordinary small diodes typically are visible in indoor lighting when they carry more than 1 mA and glow nicely at 5-10 mA. Ultrabright LEDs might draw 100 mA or more.

The voltage across the resistor is  $V_{in} - V_D$  because of the voltage drop across the diode, and it is also  $R^*I_D$  because the current flowing through the diode also flows through the resistor. Equating these two, we find  $R = (V_{in} - V_D)/I_D$ . If R is too large, the diode will be too dim. If R is too small, the diode will burn out or draw too much current from the component driving Vin. Hence, resistors in the low hundreds of ohms are common in digital circuits driving LEDs.

A datasheet lists recommended operating conditions and absolute maximum ratings. The component will operate correctly within the recommended operating conditions. It is not guaranteed to be functional near the absolute maximums, but will not take permanent damage unless the maximums are exceeded.

Current always flows from high to low. Thus output current Io flows out of the chip when the output is high, and into the chip when the output is low, and therefore has opposite signs in these two situations. The sign of the current is not very interesting; the magnitude is most important.

$\rm Icc$  is the current flowing into the Vcc pin when the chip is quiescent.  $\rm I_I$  is the input leakage current flowing into an input pin. Vol and Voh are often reported for a particular Io output current. These logic levels are not guaranteed if the output current exceeds the indicated value.