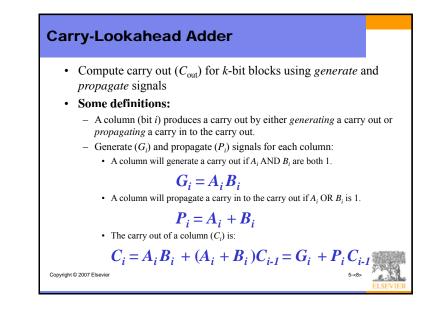

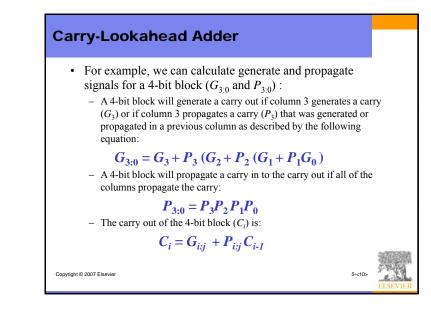

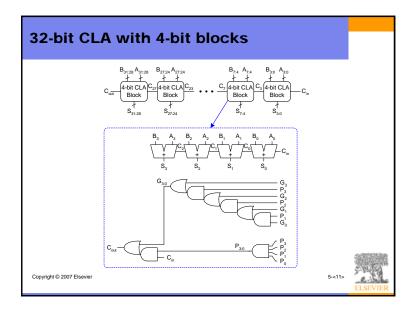

## **Carry-Lookahead Addition**

- Step 1: compute *generate* (*G*) and *propagate* (*P*) signals for columns (single bits)

- Step 2: compute *G* and *P* for *k*-bit blocks

- Step 3:  $C_{in}$  propagates through each k-bit propagate/generate block

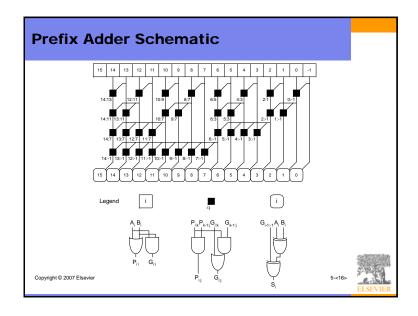

## **Prefix Adder**

• Computes the carry in (*C*<sub>*i*-1</sub>) for each of the columns as fast as possible and then computes the sum:

## $S_i = (A_i \oplus B_i) \oplus C_i$

- Computes *G* and *P* for 1-bit, then 2-bit blocks, then 4-bit blocks, then 8-bit blocks, etc. until the carry in (generate signal) is known for each column

- Has  $\log_2 N$  stages

## **Prefix Adder**

- A carry in is produced by being either *generated* in a column or *propagated* from a previous column.

- Define column -1 to hold  $C_{in}$ , so  $G_{-1} = C_{in}, P_{-1} = 0$

- Then, the carry in to column *i* = the carry out of column *i*-1:  $C_{i,1} = G_{i,1:1}$

$G_{i-1:-1}$  is the generate signal spanning columns *i*-1 to -1. There will be a carry out of column *i*-1 ( $C_{i-1}$ ) if the block spanning columns *i*-1 through -1 generates a carry.

• Thus, we can rewrite the sum equation as:

### $S_i = (A_i \bigoplus B_i) \bigoplus G_{i\text{-}1\text{:-}1}$

• **Goal:** Quickly compute  $G_{0:-1}$ ,  $G_{1:-1}$ ,  $G_{2:-1}$ ,  $G_{3:-1}$ ,  $G_{4:-1}$ ,  $G_{5:-1}$ , Copyright © 2007 E Sthese are called the *prefixes*)

## **Prefix Adder**

Copyright © 2007 Elsevie

• The generate and propagate signals for a block spanning bits *i*:*j* are:

# $G_{i:j} = G_{i:k} + P_{i:k} G_{k-1:j}$ $P_{i:j} = P_{i:k} P_{k-1:j}$

- In words, these prefixes describe that:

- A block will generate a carry if the upper part (*i*:*k*) generates a carry or if the upper part propagates a carry generated in the lower part (*k*-1;*j*)

- A block will propagate a carry if both the upper and lower parts propagate the carry.

| Copyright © 2007 Elsevier | 5~<15> | ELSEVI |

|---------------------------|--------|--------|

|                           |        |        |

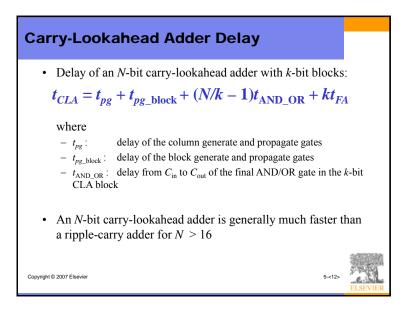

## **Prefix Adder Delay**

• The delay of an *N*-bit prefix adder is:  $t_{PA} = t_{pg} + \log_2 N(t_{pg\_prefix}) + t_{XOR}$

#### where

Copyright © 2007 Elsevier

- $t_{pg}$  is the delay of the column generate and propagate gates (AND or OR gate)

- $t_{pg_{prefix}}$  is the delay of the black prefix cell (AND-OR gate)

| <17> | ER |

|------|----|

|------|----|

5-

## **Adder Delay Comparisons**

• Compare the delay of 32-bit ripple-carry, carry-lookahead, and prefix adders. The carry-lookahead adder has 4-bit blocks. Assume that each two-input gate delay is 100 ps and the full adder delay is 300 ps.

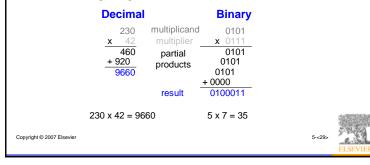

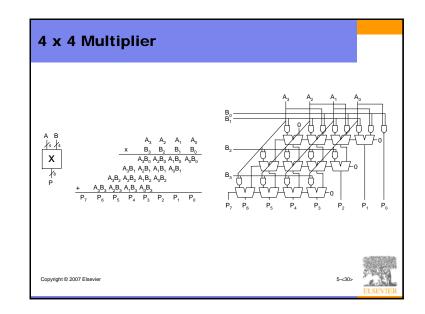

## **Multipliers**

- Steps of multiplication for both decimal and binary numbers:

- Partial products are formed by multiplying a single digit of the multiplier with the entire multiplicand

- Shifted partial products are summed to form the result

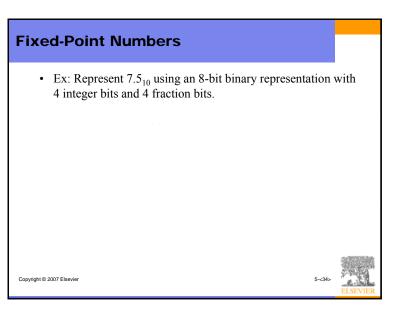

## **Fixed-Point Numbers**

• Fixed-point representation of 6.75 using 4 integer bits and 4 fraction bits:

> 01101100 0110,1100  $2^{2} + 2^{1} + 2^{-1} + 2^{-2} = 6.75$

- The binary point is not a part of the representation but is implied.

- The number of integer and fraction bits must be agreed upon by those generating and those reading the number. Copyright © 2007 Elsevier 5-<33>

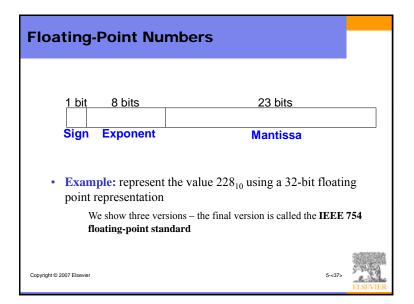

## **Floating-Point Numbers**

- The binary point floats to the right of the most significant 1.

- Similar to decimal scientific notation.

- For example, write  $273_{10}$  in scientific notation:

#### $273 = 2.73 \times 10^2$

• In general, a number is written in scientific notation as:

#### $\pm M \times B^E$

- **M** = mantissa

- **B** = base

- $-\mathbf{E} = exponent$

- In the example, M = 2.73, B = 10, and E = 2

#### Copyright © 2007 Elsevier

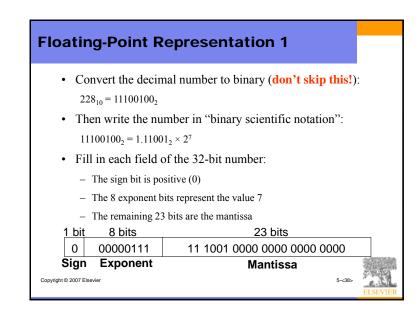

| Floating-Point Rep                                                                                                          | presentation 2                        |          |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------|

| <ul> <li>228<sub>10</sub> = 11100100<sub>2</sub> =</li> <li>Thus, storing the moleading <i>1</i>, is redundated.</li> </ul> | ost significant 1, also called the im |          |

| 1 bit 8 bits                                                                                                                | 23 bits                               |          |

| 0 00000111                                                                                                                  | 110 0100 0000 0000 0000 000           | 0        |

| Sign Exponent                                                                                                               | Fraction<br>5-<39>                    | ELSEVIER |

| Float                  | ing-Point I           | Representation 3                                                |

|------------------------|-----------------------|-----------------------------------------------------------------|

| • )                    | Biased exponent       | $bias = 127 (01111111_2)$                                       |

|                        | - Biased exponen      | t = bias + exponent                                             |

|                        | - Exponent of 7 is    | s stored as:                                                    |

|                        | 127 -                 | $-7 = 134 = 0 \times 10000110_2$                                |

| • 7                    | The <b>IEEE 754 3</b> | <b>2-bit floating-point representation</b> of 228 <sub>10</sub> |

| <u>1 bit</u>           | 8 bits                | 23 bits                                                         |

| 0                      | 10000110              | 110 0100 0000 0000 0000 0000                                    |

| Sign                   | Biased<br>Exponent    | Fraction                                                        |

| • ]<br>Copyright © 200 | n hexadecimal: 0x4    | 43640000<br>5-<40>                                              |

### Floating-Point Numbers: Special Cases

• The IEEE 754 standard includes special cases for numbers that are difficult to represent, such as 0 because it lacks an implicit leading 1.

| Number              | Sign     | Exponent       | Fraction                                     |

|---------------------|----------|----------------|----------------------------------------------|

| 0                   | Х        | 00000000       | 000000000000000000000000000000000000000      |

| x                   | 0        | 11111111       | 000000000000000000000000000000000000000      |

| - ∞                 | 1        | 11111111       | 000000000000000000000000000000000000000      |

| NaN                 | Х        | 11111111       | non-zero                                     |

| NaN is              | used for | numbers that o | don't exist, such as $\sqrt{-1}$ or log(-5). |

| pht © 2007 Elsevier |          |                | 5-<42>                                       |

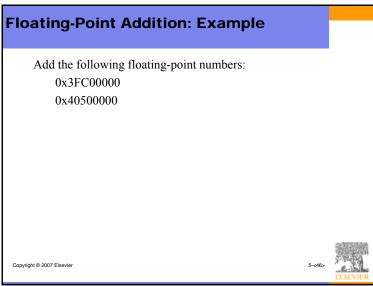

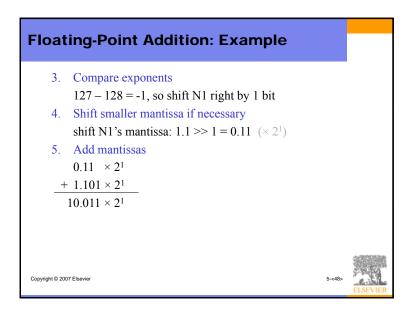

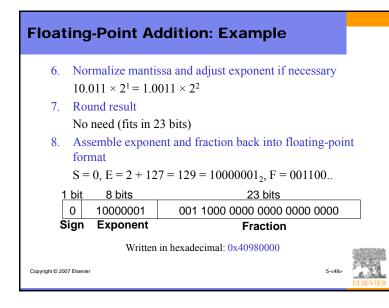

| Float           | ting-Point Addition: Example                                                                                                                                    |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.              | Extract exponent and fraction bits                                                                                                                              |

|                 | 0         01111111         100 0000 0000 0000 0000           Sign         Exponent         Fraction                                                             |

|                 | 1 bit         8 bits         23 bits           0         10000000         101 0000 0000 0000 0000         0000           Sign         Exponent         Fraction |

|                 | For first number (N1): $S = 0, E = 127, F = .1$                                                                                                                 |

| 2.              | For second number (N2): $S = 0, E = 128, F = .101$<br>Prepend leading 1 to form mantissa                                                                        |

|                 | N1: 1.1<br>N2: 1.101                                                                                                                                            |

| Copyright © 200 |                                                                                                                                                                 |

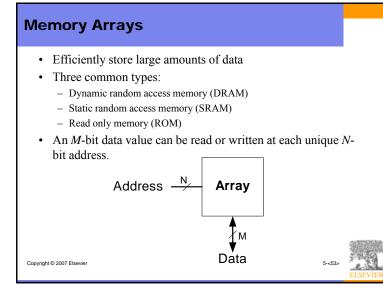

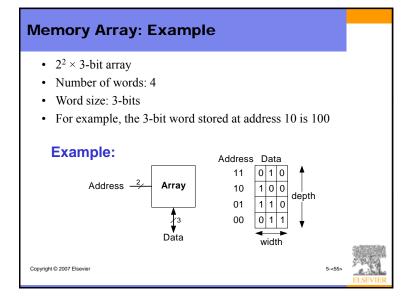

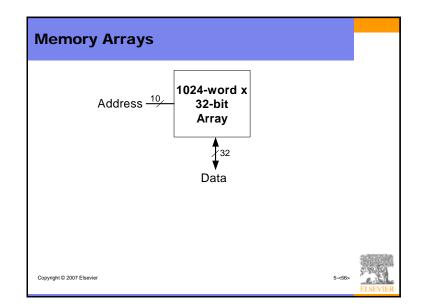

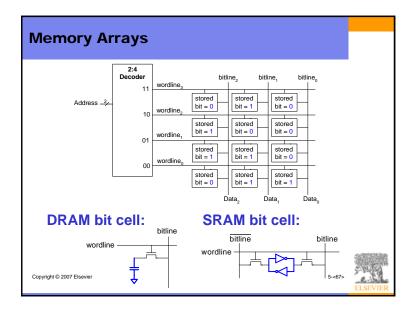

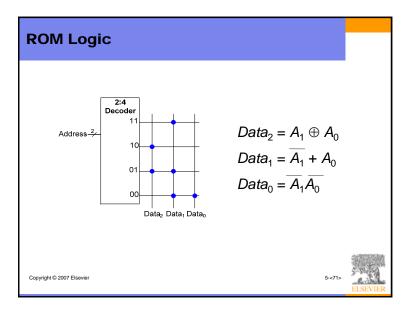

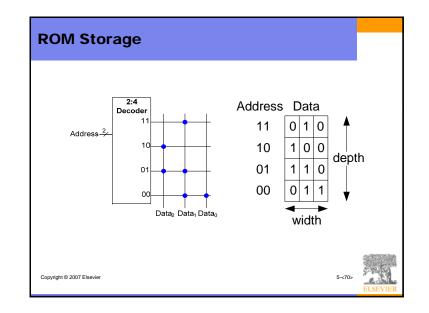

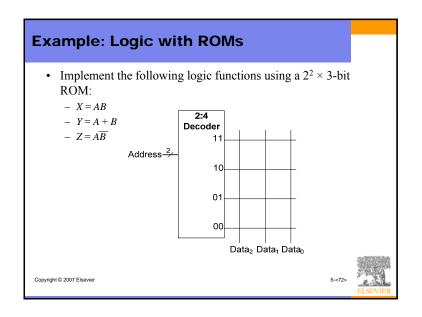

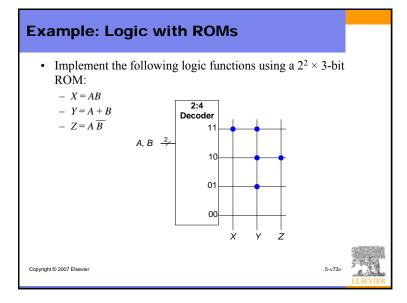

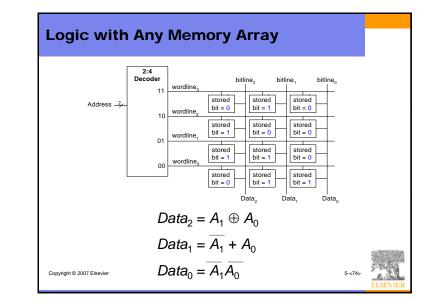

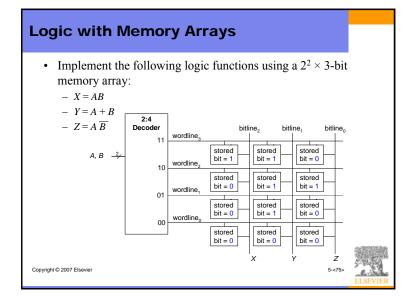

#### **Memory Arrays** • Two-dimensional array of bit cells • Each bit cell stores one bit • An array with *N* address bits and *M* data bits: $-2^N$ rows and *M* columns - **Depth:** number of rows (number of words) - Width: number of columns (size of word) - Array size: depth $\times$ width = $2^N \times M$ Address Data 11 010 Address -2/ Array Address – N Array 10 100 depth 01 1 1 ₹3 00 0 1 ₹M Data Data widt Copyright © 2007 Elsevier

## **Types of Memory**

- Random access memory (RAM): volatile

- Read only memory (ROM): nonvolatile

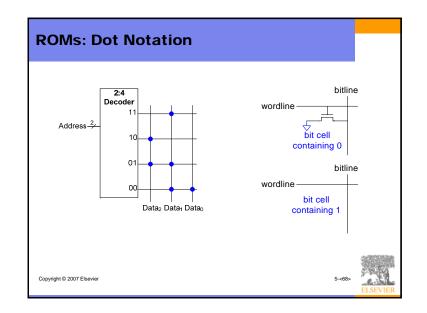

## **ROM: Read Only Memory**

- Nonvolatile: retains data when power is turned off

- Read quickly, but writing is impossible or slow

- Flash memory in cameras, thumb drives, and digital cameras are all ROMs

Historically called *read only* memory because ROMs were written at manufacturing time or by burning fuses. Once ROM was configured, it could not be written again. This is no longer the case for Flash memory and other types of ROMs.

Copyright © 2007 Elsevier

Copyright © 2007 Elsevie

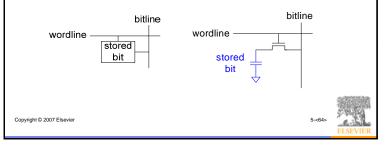

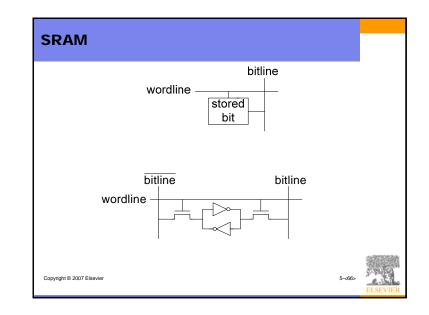

## Types of RAM

- Two main types of RAM:

- Dynamic random access memory (DRAM)

- Static random access memory (SRAM)

- Differ in how they store data:

- DRAM uses a capacitor

- SRAM uses cross-coupled inverters

## Robert Dennard, 1932 -

- Invented DRAM in 1966 at IBM

- Others were skeptical that the idea would work

- By the mid-1970's DRAM was in virtually all computers

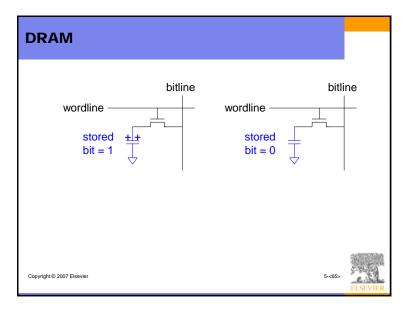

## DRAM

Copyright © 2007 Elsevier

- Data bits stored on a capacitor

- Called *dynamic* because the value needs to be refreshed (rewritten) periodically and after being read:

- Charge leakage from the capacitor degrades the value

- Reading destroys the stored value

## Fujio Masuoka, 1944-

- Developed memories and high speed circuits at Toshiba from 1971-1994.

- Invented Flash memory as an unauthorized project pursued during nights and weekends in the late 1970's.

- The process of erasing the memory reminded him of the flash of a camera

- Toshiba slow to commercialize the idea; Intel was first to market in 1988

- Flash has grown into a \$25 billion per year market.

Copyright © 2007 Elsevier

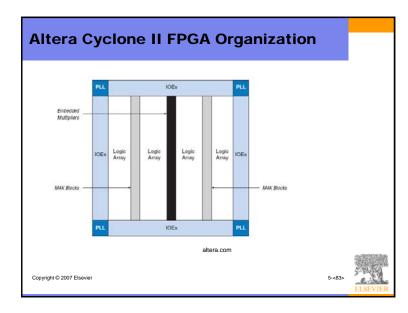

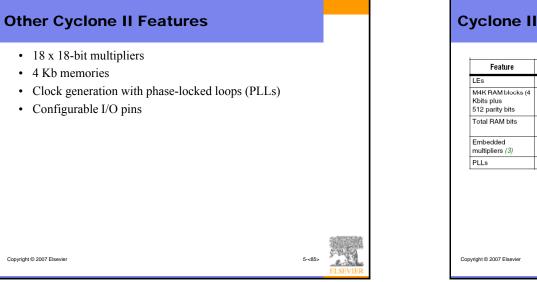

| Feature                                            | EP2C5 (2) | EP2C8 (2) | EP2C15 (1) | EP2C20 (2) | EP2C35  | EP2C50     | EP2C7       |

|----------------------------------------------------|-----------|-----------|------------|------------|---------|------------|-------------|

| LEs                                                | 4,608     | 8,256     | 14,448     | 18,752     | 33,216  | 50,528     | 68,41       |

| M4K RAM blocks (4<br>Kbits plus<br>512 parity bits | 26        | 36        | 52         | 52         | 105     | 129        | 250         |

| Total RAM bits                                     | 119,808   | 165,888   | 239,616    | 239,616    | 483,840 | 594,432    | 1,152,<br>0 |

| Embedded<br>multipliers (3)                        | 13        | 18        | 26         | 26         | 35      | 86         | 150         |

| PLLs                                               | 2         | 2         | 4          | 4          | 4       | 4          | 4           |

|                                                    |           |           |            |            |         | altera.com |             |

| Feature                               | Strati | x V GT | ſ |  |

|---------------------------------------|--------|--------|---|--|

| reature                               | 5SGTB5 | 5SGTB7 | í |  |

| Logic Elements                        | 425K   | 622K   | 1 |  |

| Registers                             | 642K   | 939K   |   |  |

| 28G Transceivers (maximum rate)       | 4      | 4      |   |  |

| 12.5G Transceivers (maximum rate)     | 32     | 32     |   |  |

| Embedded Hardcopy Blocks              | 1      | 1      |   |  |

| Fractional PLLs                       | 24     | 24     |   |  |

| Memory Blocks (20 Kbits each)         | 2,304  | 2,560  |   |  |

| Total Memory (Mbits)                  | 45     | 50     |   |  |

| Variable Precision Multipliers—18×18  | 512    | 512    |   |  |

| Variable Precision Multipliers —27×27 | 256    | 256    |   |  |

| DDR3 SDRAM ×72 DIMM Interfaces        | 4      | 4      |   |  |

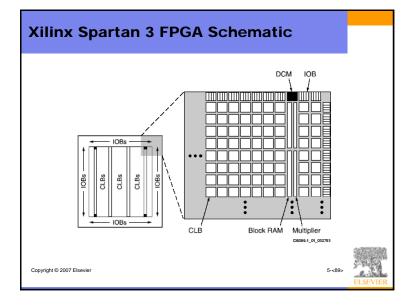

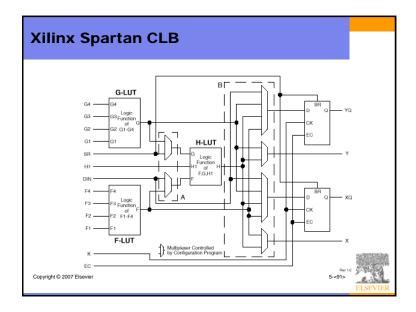

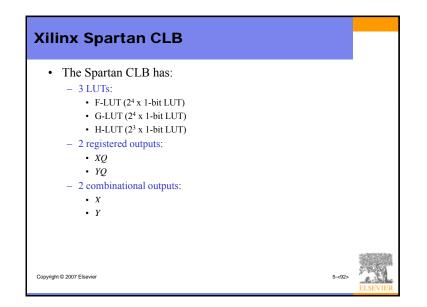

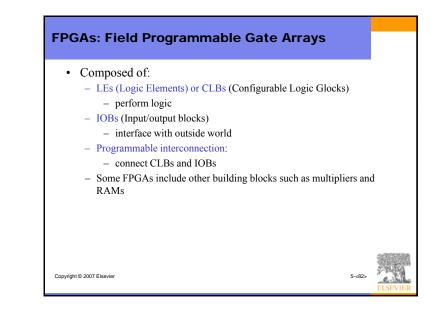

# FPGA Design Flow A CAD tool (such as Altera's Quartus or Xilinx's Project Navigator) is used to design and implement a digital system. It is usually an iterative process. The user enters the design using schematic entry or an HDL. The user simulates the design. A synthesis tool converts the code into hardware and maps it onto the FPGA. The user uses the CAD tool to download the configuration onto the FPGA

• This configures the CLBs and the connections between them and the IOBs.

Copyright © 2007 Elsevier