### Introduction

Copyright © 2007 Elsevie

- Outputs of sequential logic depend on current *and* prior input values it has *memory*.

- Some definitions:

- State: all the information about a circuit necessary to explain its future behavior

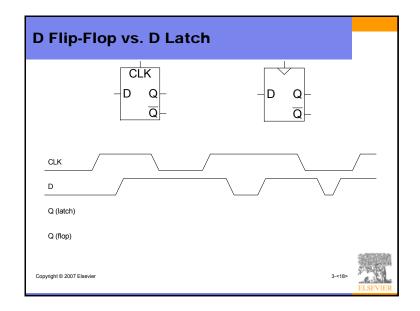

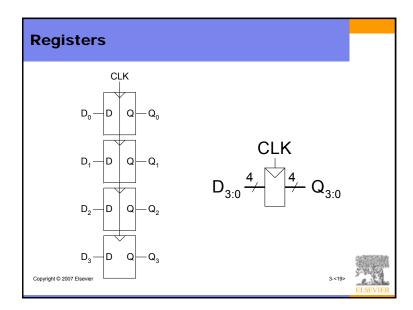

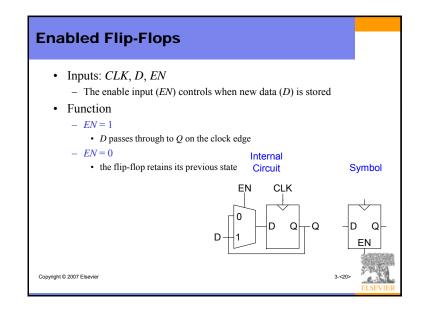

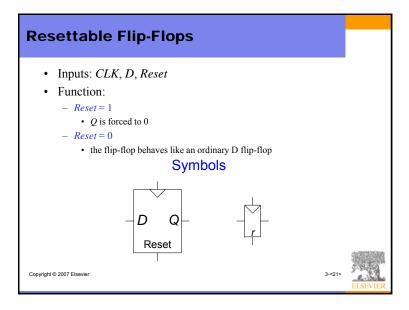

- Latches and flip-flops: state elements that store one bit of state

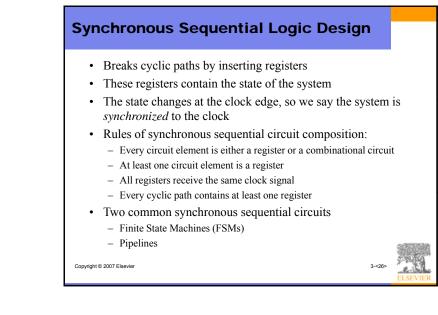

- Synchronous sequential circuits: combinational logic followed by a bank of flip-flops

## 3.≺

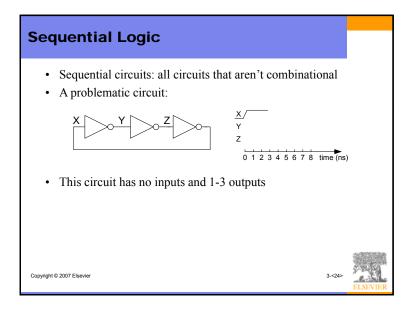

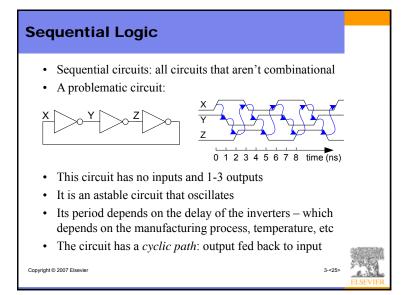

### **Sequential Circuits**

- Give sequence to events

- Have memory (short-term)

- Use feedback from output to input to store information

Copyright © 2007 Elsevier

### **State Elements**

- The state of a circuit influences its future behavior

- State elements store state

- Bistable circuit

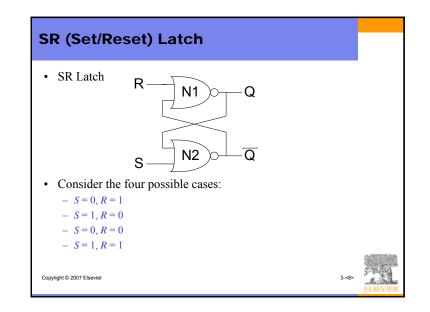

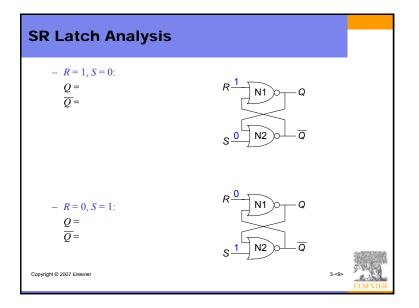

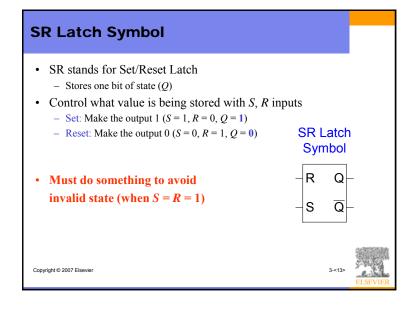

- SR Latch

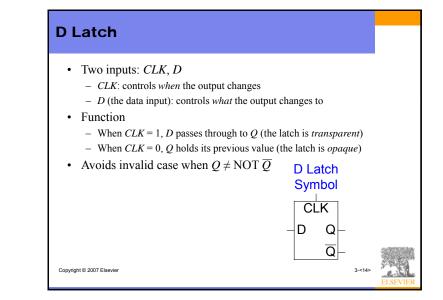

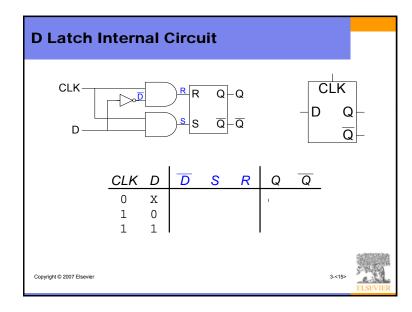

- D Latch

Copyright © 2007 Elsevier

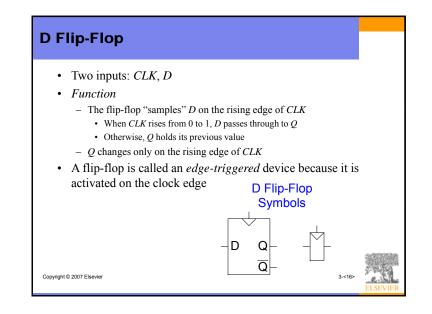

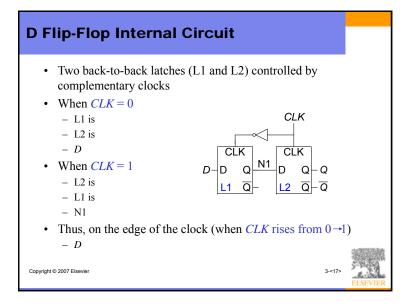

– D Flip-flop

| 3-<5> | ELSEVIER |

|-------|----------|

|-------|----------|

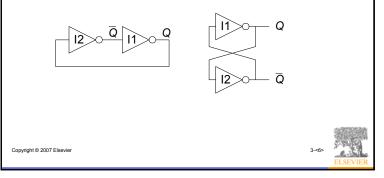

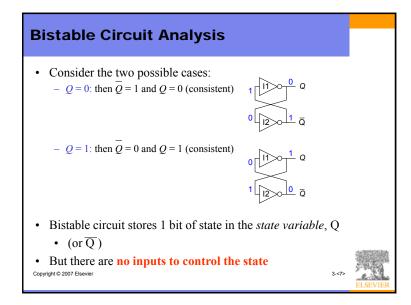

### **Bistable Circuit**

- Fundamental building block of other state elements

- Two outputs:  $Q, \overline{Q}$

- No inputs

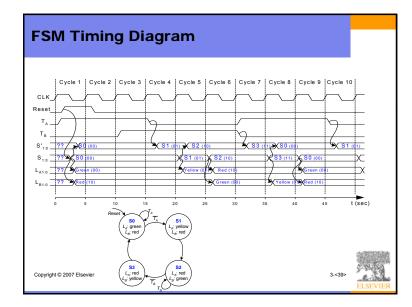

| FS     | SM O             | utput | Tab                                                  | le       |          |          |   |        |                  |

|--------|------------------|-------|------------------------------------------------------|----------|----------|----------|---|--------|------------------|

| ſ      | Current State    |       | Outputs                                              |          |          |          | ] | 0.1.1  | <b>D</b> 1'      |

|        | $S_1$            | $S_0$ | $L_{A1}$                                             | $L_{A0}$ | $L_{B1}$ | $L_{B0}$ |   | Output | Encoding         |

|        | 0                | 0     |                                                      |          |          |          |   | green  | 00               |

|        | 0                | 1     |                                                      |          |          | 1        |   | yellow | 01               |

|        | 1                | 0     |                                                      |          |          | 1        |   | -      | 10               |

|        | 1                | 1     |                                                      |          |          |          |   | red    | 10               |

| _      |                  |       | $L_{A1} =$<br>$L_{A0} =$<br>$L_{B1} =$<br>$L_{B0} =$ |          |          |          | _ |        |                  |

| Copyri | ight © 2007 Else | evier | $L_{B0}^{B1} =$                                      |          |          |          |   |        | 3-<35><br>ELSEVI |

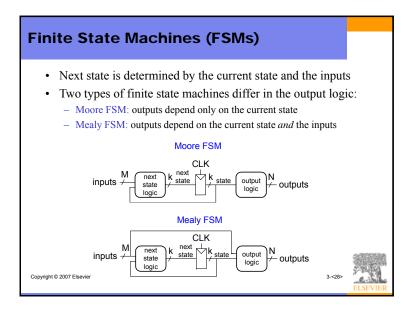

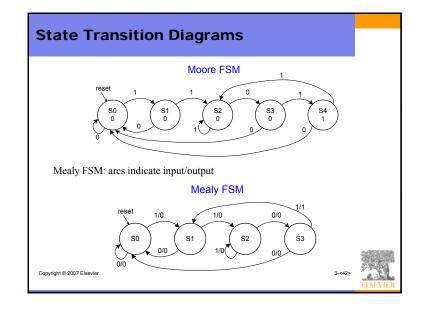

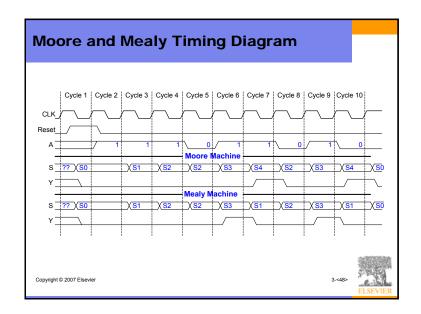

# Moore vs. Mealy FSM • Alyssa P. Hacker has a snail that crawls down a paper tape with 1's and 0's on it. The snail smiles whenever the last four digits it has crawled over are 1101. Design Moore and Mealy FSMs of the snail's brain.

| Cu    | rent S | State | Inputs | Next State |        |        |       |         |

|-------|--------|-------|--------|------------|--------|--------|-------|---------|

| $S_2$ | $S_1$  | $S_0$ | Α      | $S'_2$     | $S'_1$ | $S'_0$ |       |         |

| 0     | 0      | 0     | 0      |            |        |        | State | Encodin |

| 0     | 0      | 0     | 1      |            |        |        | S0    | 000     |

| 0     | 0      | 1     | 0      |            | 1      |        |       |         |

| 0     | 0      | 1     | 1      |            |        | 1      | S1    | 001     |

| 0     | 1      | 0     | 0      |            |        | _      | S2    | 010     |

| 0     | 1      | 0     | 1      |            |        |        |       |         |

| 0     | 1      | 1     | 0      |            | 1      | -      | S3    | 011     |

| 0     | 1      | 1     | 1      |            |        |        | S4    | 100     |

| 1     | 0      | 0     | 0      |            | 1      |        | 5.    | 100     |

| 1     | 0      | 0     | 1      |            | i      | 1      |       |         |

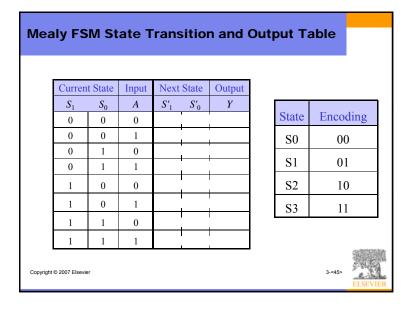

| Cu    | Current State |       |   |     |  |

|-------|---------------|-------|---|-----|--|

| $S_2$ | $S_1$         | $S_0$ | Y |     |  |

| 0     | 0             | 0     | - |     |  |

| 0     | 0             | 1     | - | Y = |  |

| 0     | 1             | 0     | - |     |  |

| 0     | 1             | 1     | - |     |  |

| 1     | 0             | 0     | - |     |  |

|       |               |       |   |     |  |

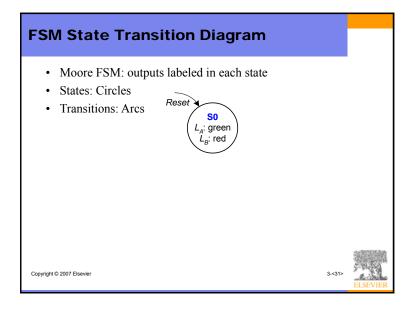

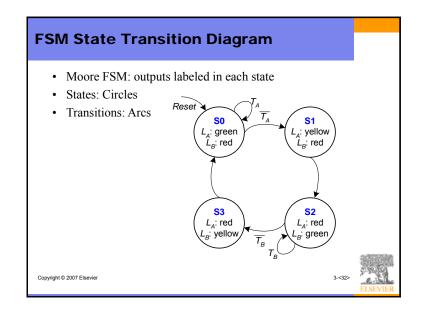

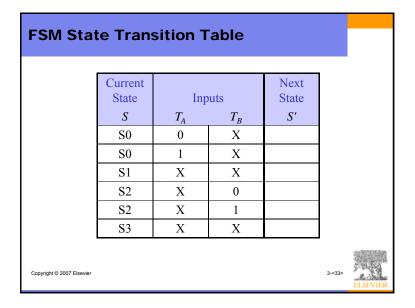

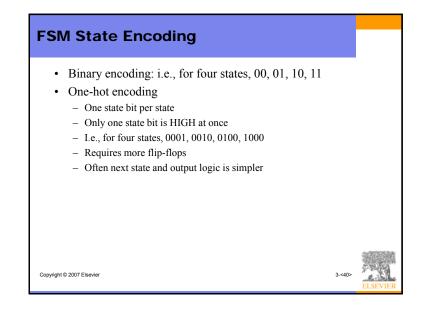

- Identify the inputs and outputs

- Sketch a state transition diagram

- Write a state transition table

- Select state encodings

- For a Moore machine:

- Rewrite the state transition table with the selected state encodings

- Write the output table

- For a Mealy machine:

Copyright © 2007 Elsevier

- Rewrite the combined state transition and output table with the selected state encodings

- Write Boolean equations for the next state and output logic

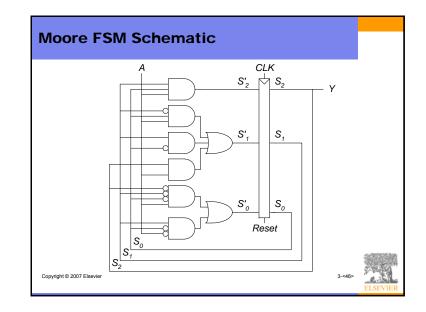

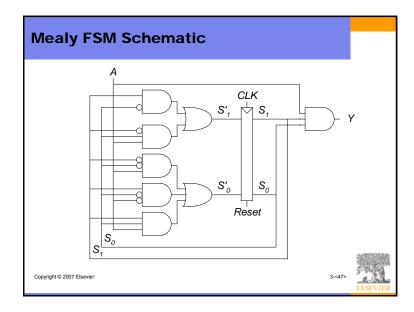

- Sketch the circuit schematic

| <53><br>ELSEVIER |  |

|------------------|--|

|------------------|--|

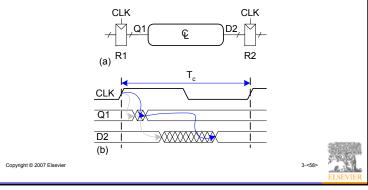

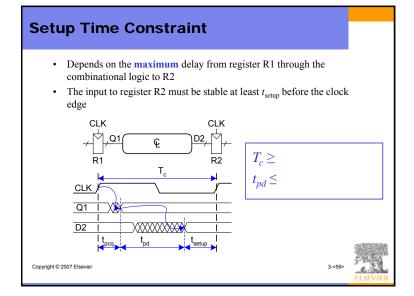

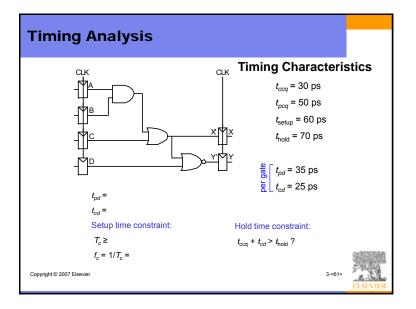

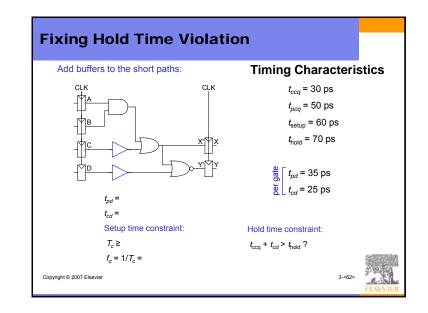

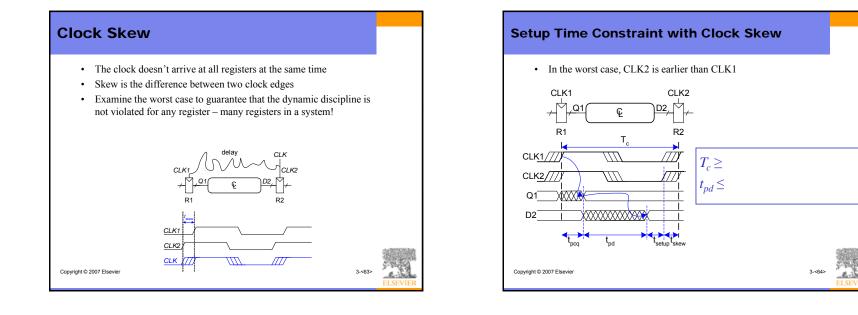

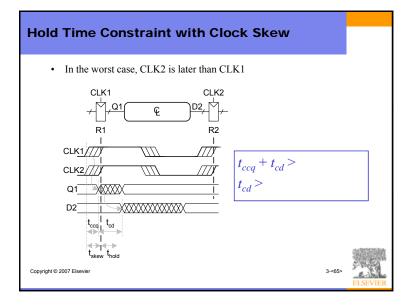

### Timing

Copyright © 2007 Elsevie

- Flip-flop samples *D* at clock edge

- *D* must be stable when it is sampled

- Similar to a photograph, *D* must be stable around the clock edge

- If *D* is changing when it is sampled, metastability can occur

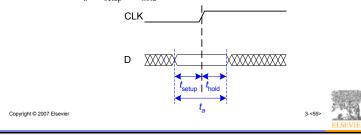

### **Input Timing Constraints**

- Setup time: *t*<sub>setup</sub> = time *before* the clock edge that data must be stable (i.e. not changing)

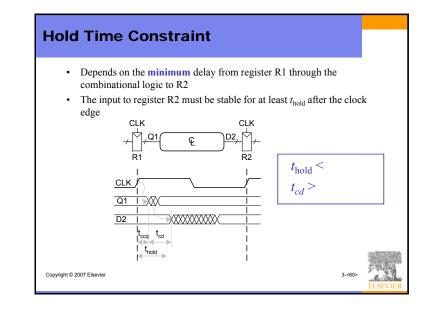

- **Hold time:**  $t_{hold}$  = time *after* the clock edge that data must be stable

- Aperture time:  $t_a$  = time around clock edge that data must be stable ( $t_a = t_{setup} + t_{hold}$ )

# Output Timing Constraints Propagation delay: t<sub>pcq</sub> = time after clock edge that the output Q is guaranteed to be stable (i.e., to stop changing) Contamination delay: t<sub>ccq</sub> = time after clock edge that Q might be unstable (i.e., start changing) CLK Q

### **Dynamic Discipline**

Copyright © 2007 Elsevie

- The input to a synchronous sequential circuit must be stable during the aperture (setup and hold) time around the clock edge.

- Specifically, the input must be stable

- at least  $t_{setup}$  before the clock edge

- at least until  $t_{hold}$  after the clock edge

### **Dynamic Discipline**

• The delay between registers has a **minimum** and **maximum** delay, dependent on the delays of the circuit elements

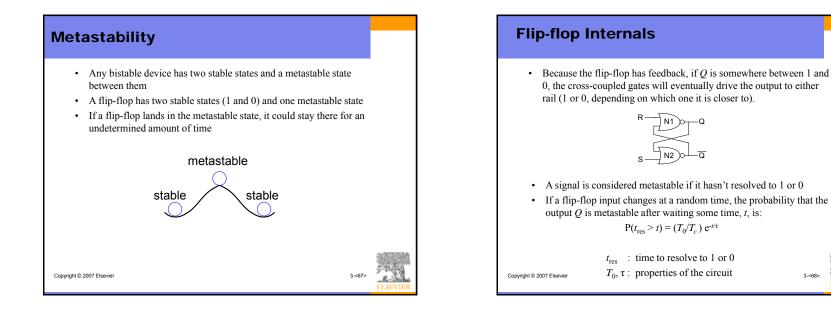

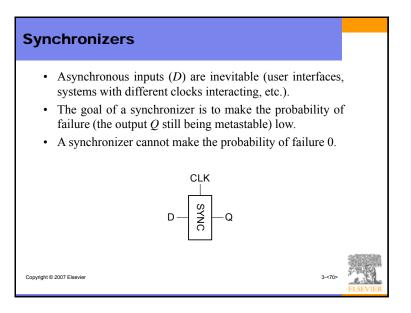

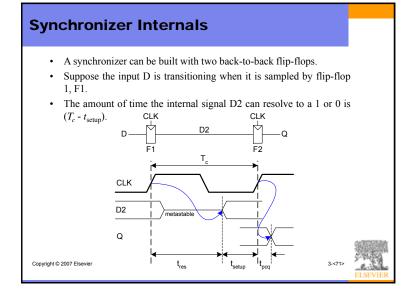

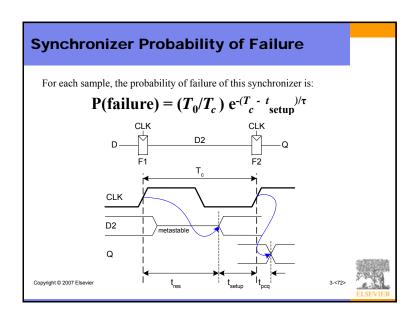

### Metastability

- Intuitively:

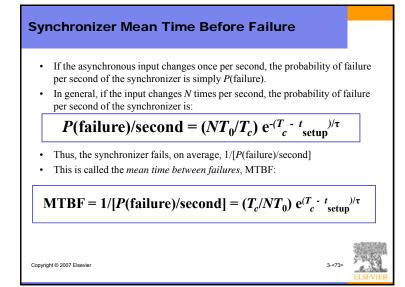

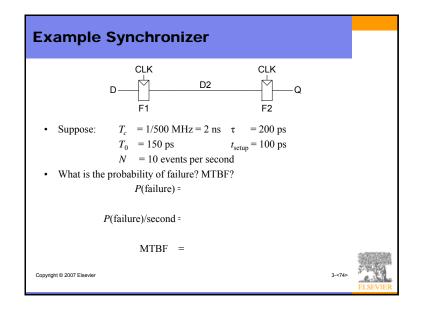

- $T_0/T_{\rm c}$  describes the probability that the input changes at a bad time, i.e., during the aperture time

$P(t_{res} > t) = (T_0/T_c) e^{-t/\tau}$

$-\tau$  is a time constant indicating how fast the flip-flop moves away from the metastable state; it is related to the delay through the cross-coupled gates in the flip-flop

$$\mathbf{P}(t_{\rm res} > t) = (T_0/T_c) \, \mathrm{e}^{-t/\tau}$$

• In short, if a flip-flop samples a metastable input, if you wait long enough (*t*), the output will have resolved to 1 or 0 with high probability.

Copyright © 2007 Elsevier

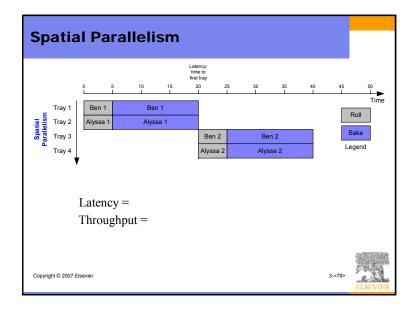

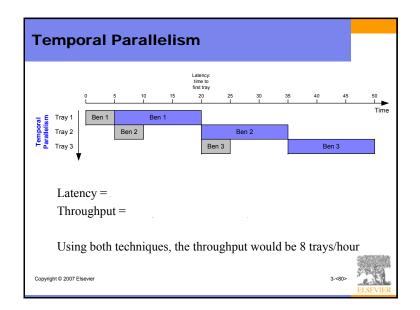

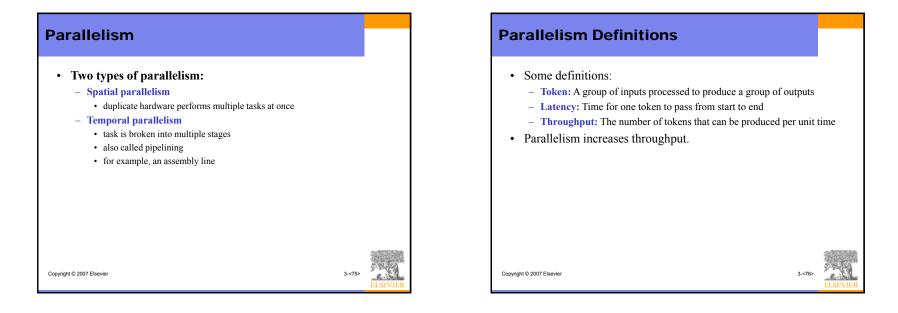

### **Parallelism Example**

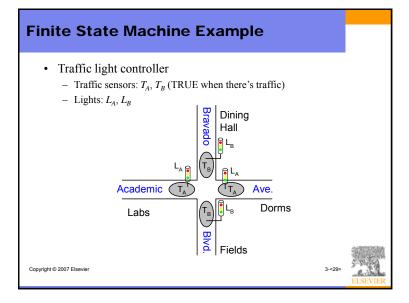

• Ben Bitdiddle is baking cookies to celebrate the installation of his traffic light controller. It takes 5 minutes to roll the cookies and 15 minutes to bake them. After finishing one batch he immediately starts the next batch. What is the latency and throughput if Ben doesn't use parallelism?

# **Darallelism Example**What is the latency and throughput if Ben uses parallelism? Spatial parallelism? Ben asks Allysa P. Hacker to help, using her own oven Temporal parallelism? Ben breaks the task into two stages: roll and baking. He uses two trays. While the first batch is baking he rolls the second batch, and so on.