# Lecture 23: I/O

### Outline

- Basic I/O Pads

- I/O Channels

- Transmission Lines

- Noise and Interference

- □ High-Speed I/O

- Transmitters

- Receivers

- Clock Recovery

- Source-Synchronous

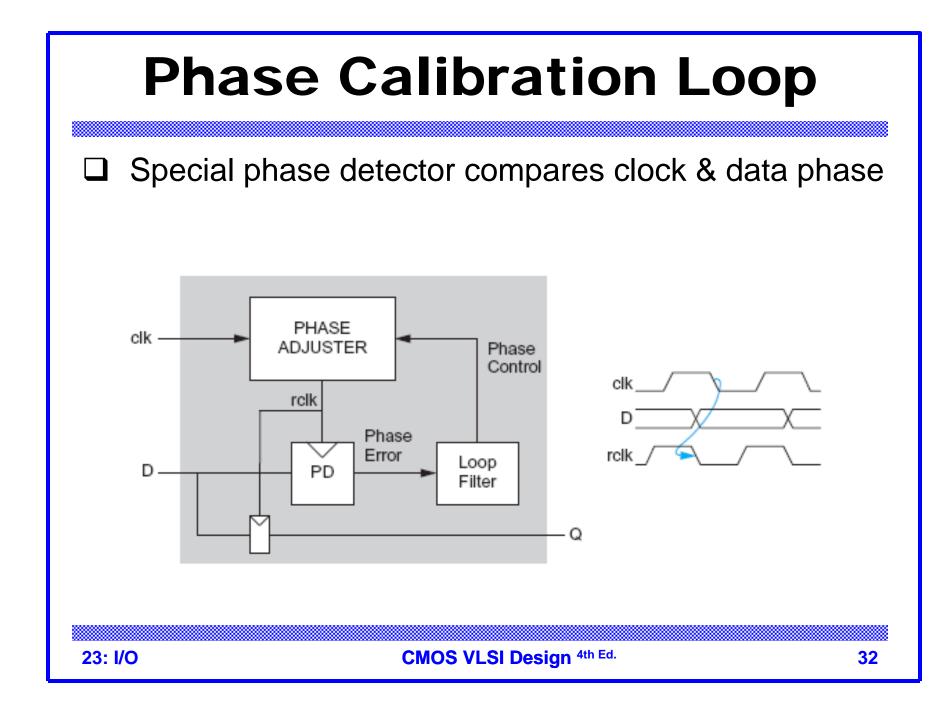

- Mesochronous

# Input / Output

### Input/Output System functions

- Communicate between chip and external world

- Drive large capacitance off chip

- Operate at compatible voltage levels

- Provide adequate bandwidth

- Limit slew rates to control di/dt noise

- Protect chip against electrostatic discharge

- Use small number of pins (low cost)

## I/O Pad Design

### Pad types

- $-V_{\rm DD}$  / GND

- Output

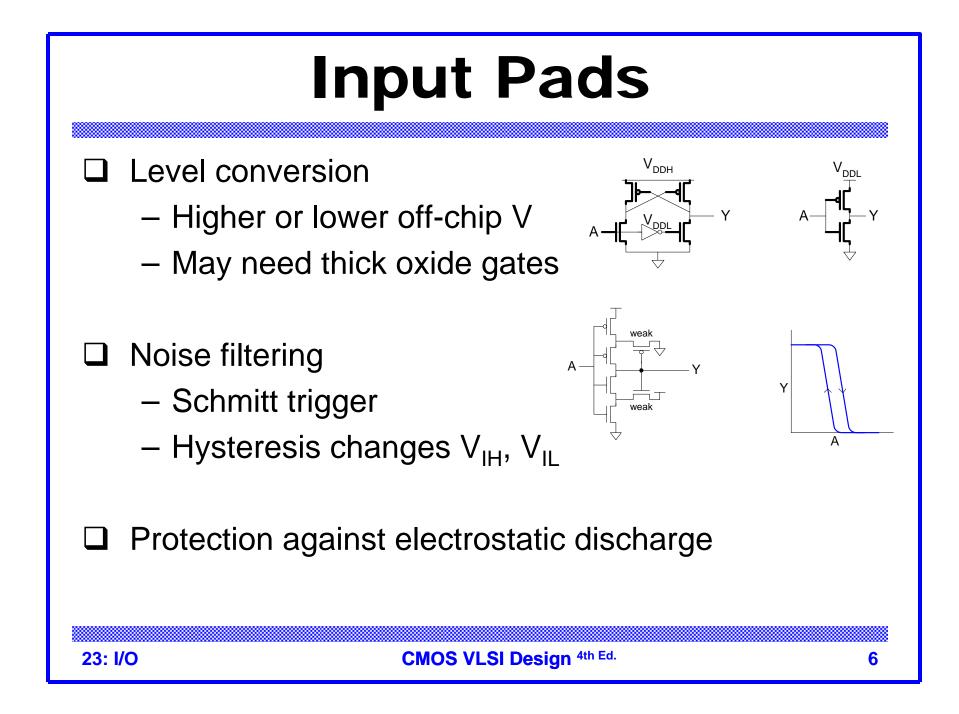

- Input

- Bidirectional

- Analog

CMOS VLSI Design <sup>4th Ed.</sup>

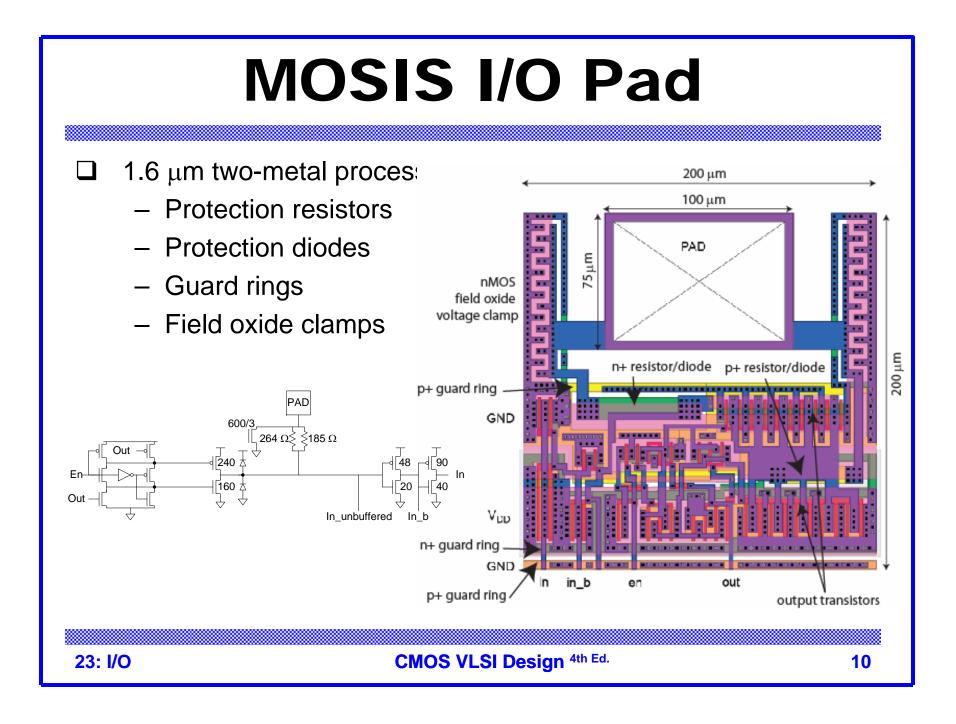

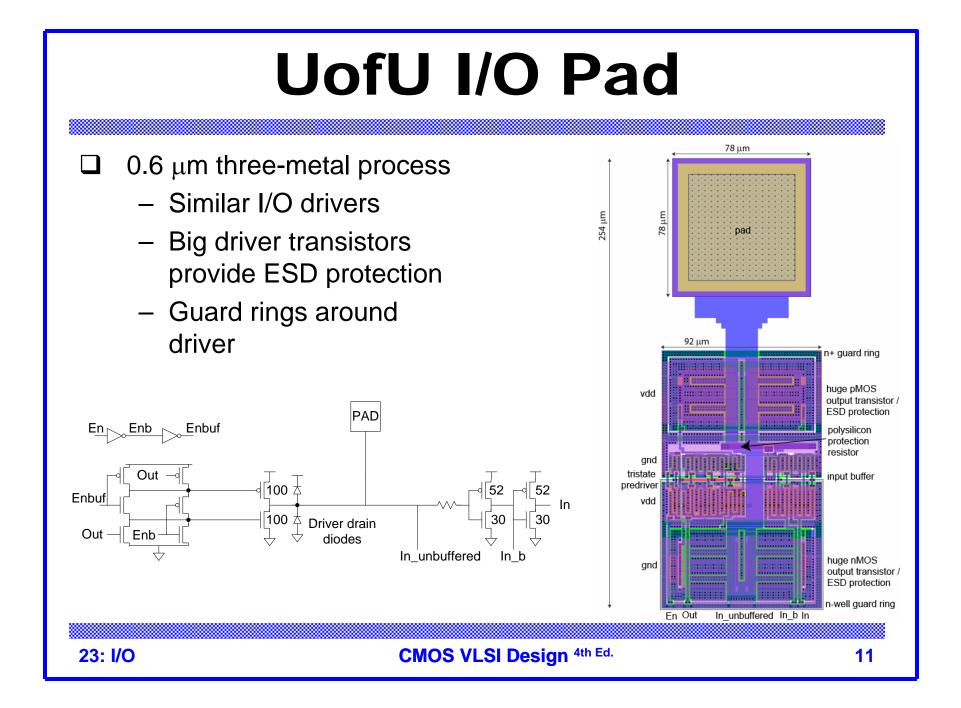

### **Output Pads**

- □ Drive large off-chip loads (2 50 pF)

- With suitable rise/fall times

- Requires chain of successively larger buffers

- Guard rings to protect against latchup

- Noise below GND injects charge into substrate

- Large nMOS output transistor

- p+ inner guard ring

- n+ outer guard ring

- In n-well

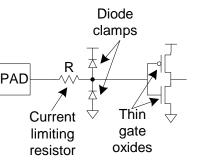

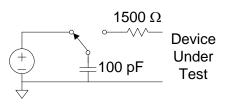

### **ESD** Protection

- □ Static electricity builds up on your body

- Shock delivered to a chip can fry thin gates

- Must dissipate this energy in protection circuits before it reaches the gates

- **ESD** protection circuits

- Current limiting resistor

- Diode clamps

- **ESD** testing

- Human body model

- Views human as charged capacitor

7

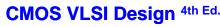

### **Bidirectional Pads**

- Combine input and output pad

- Need tristate driver on output

- Use enable signal to set direction

- Optimized tristate avoids huge series transistors

# **Analog Pads**

Pass analog voltages directly in or out of chip

- No buffering

- Protection circuits must not distort voltages

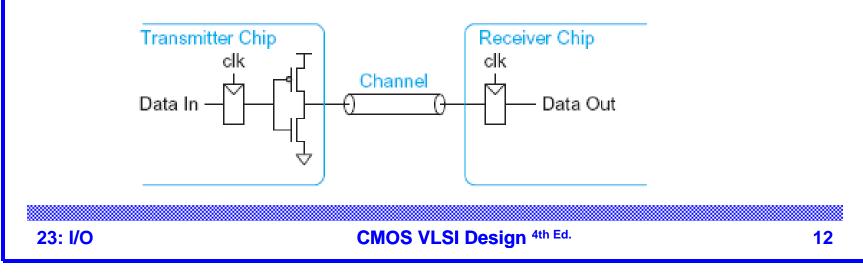

### **I/O Channels**

□ I/O Channel: connection between chips

- Low frequency: ideal equipotential net

- High frequency: transmission line

Transmission lines model

- Finite velocity of signal along wire

- Characteristic impedance of wire

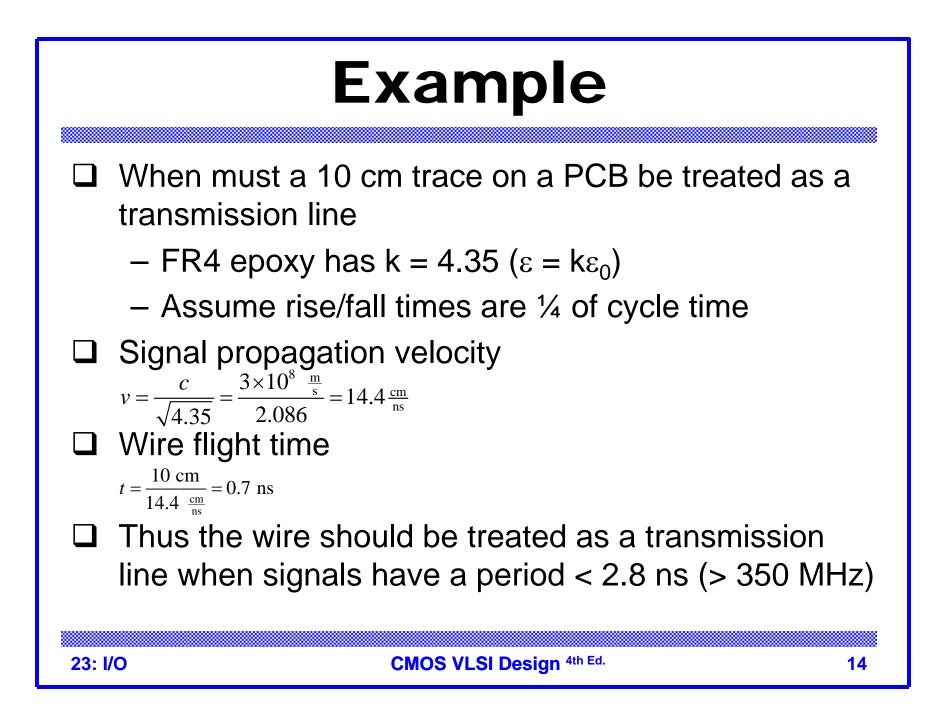

# When proposition dology along the wire in

- When propagation delay along the wire is comparable to the edge rate of the signal propagating

- Depends on

- Length

- Speed of light in the medium

- Edge rate

### Example

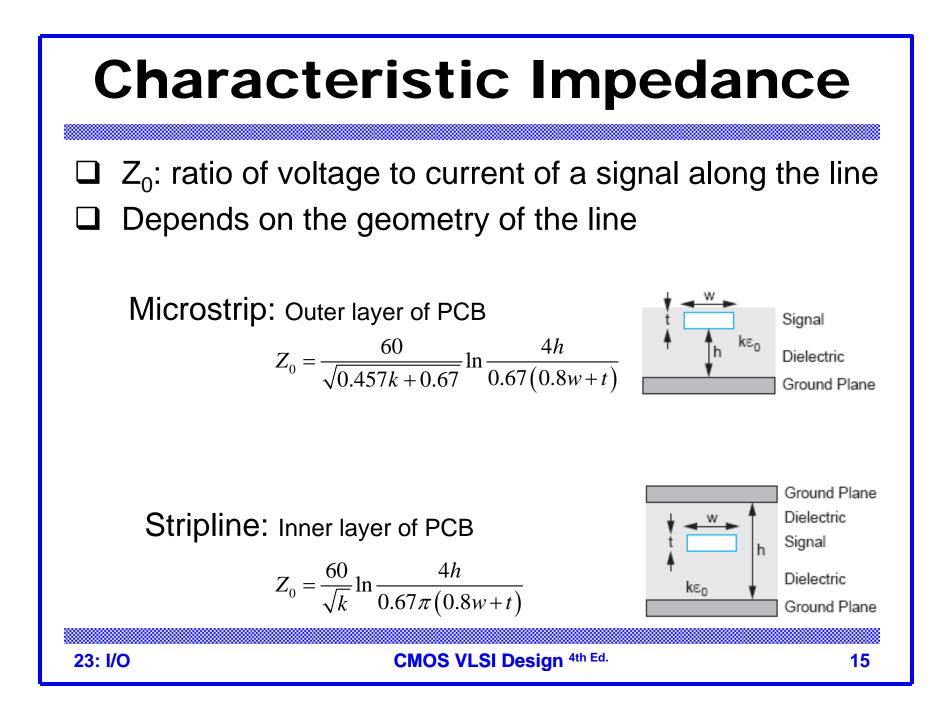

A 4-layer PCB contains power and ground planes on the inner layers and signals on the outer layers. The board uses 1 oz copper (1.4 mils thick) and the FR4 dielectric is 8.7 mils thick. How wide should the traces be to achieve 50 Ω characteristic impedance?

□ This is a microstrip design. Solve for w with

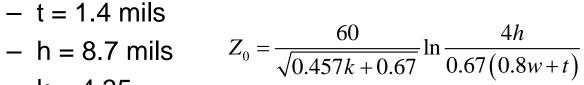

$$- K = 4.35$$

$$- Z_0 = 50 \Omega$$

**)** w = 15 mils

CMOS VLSI Design 4th Ed.

23: I/O

### Reflections

When a wave hits the end of a transmission line, part of the energy will reflect if the load impedance does not match the characteristic impedance.

Reflection coefficient:

$$\Gamma = \frac{Z_L - Z_0}{Z_L + Z_0}$$

A wave with an amplitude of  $V_{reflected} = \Gamma V_{incident}$ returns along the line.

### **Example: Reflections**

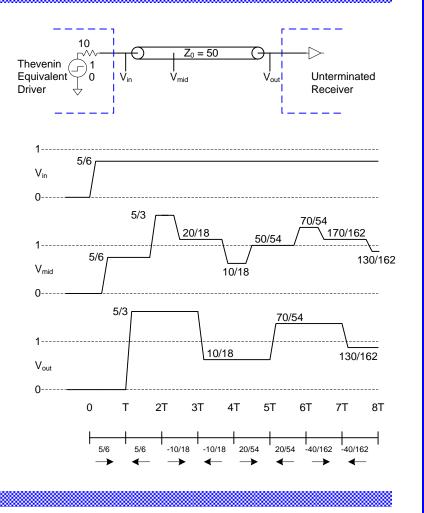

- A strong driver with a Thevenin equivalent resistance of 10  $\Omega$  drives an unterminated transmission line with  $Z_0 = 50 \Omega$  and flight time T. Plot the voltage at the 1/3 point and end of the line.

- Reflection coefficients:

$$\Gamma_s = \frac{10-50}{10+50} = -\frac{2}{3}; \ \Gamma_L = \frac{\infty-50}{\infty+50} = 1$$

□ Initial wave: 50/(10+50) = 5/6

Observe ringing at load

23: I/O

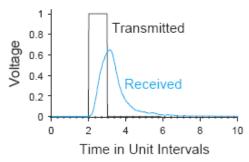

### **Intersymbol Interference**

- Must wait until reflections damp out before sending next bit

- □ Otherwise, *intersymbol interference* will occur

- With an unterminated transmission line, minimum bit time is equal to several round trips along the line

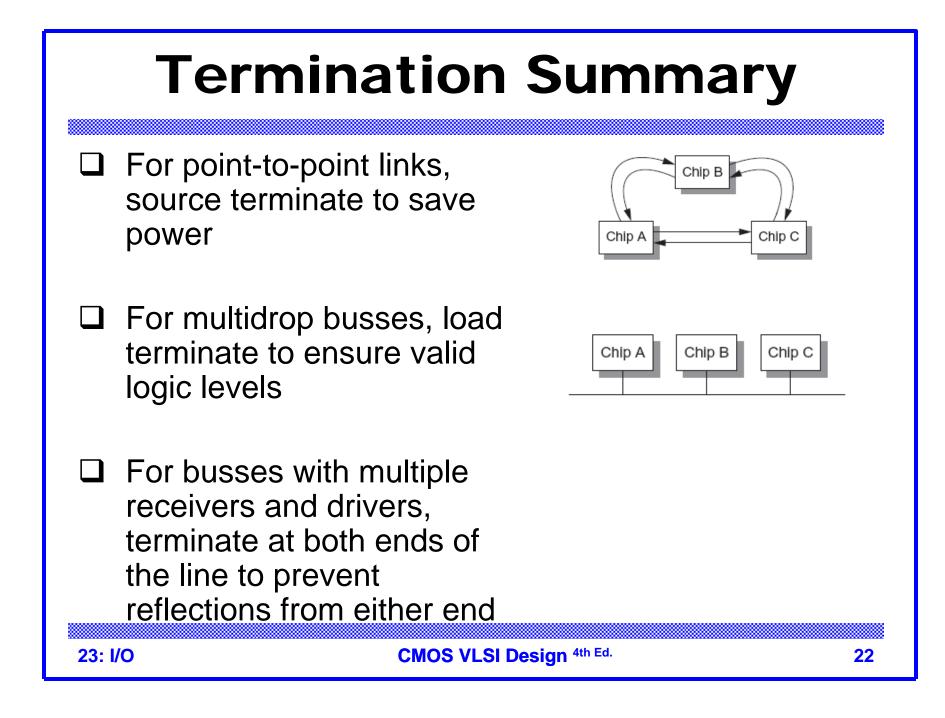

### **Example: Load Termination**

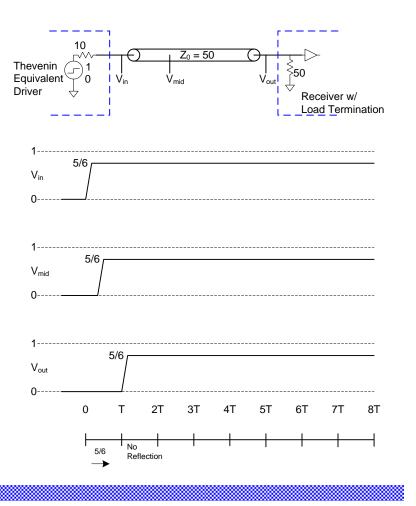

- Redo the previous example if the load is terminated with a 50 Ω resistor.

- □ Reflection coefficients:

$$\Gamma_s = \frac{10-50}{10+50} = -\frac{2}{3}; \ \Gamma_L = \frac{50-50}{50+50} = 0$$

- ☐ Initial wave: 50/(10+50) = 5/6

- No ringing

- Power dissipation in load resistor

23: I/O

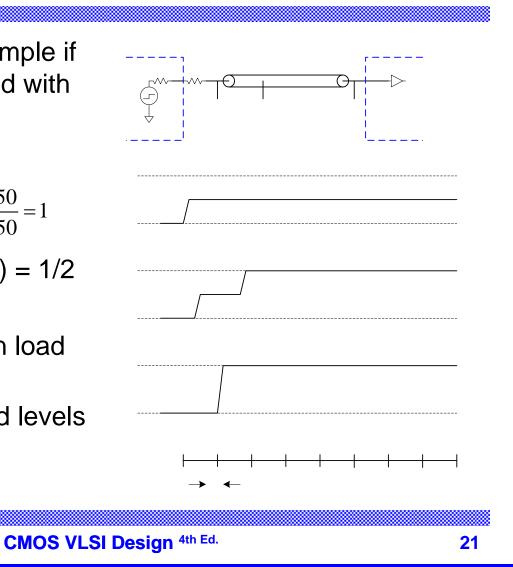

### **Example: Source Termination**

- Redo the previous example if the source is terminated with an extra 40 Ω resistor.

- □ Reflection coefficients:

$$\Gamma_s = \frac{50 - 50}{50 + 50} = 0; \ \Gamma_L = \frac{\infty - 50}{\infty + 50} = 1$$

- ☐ Initial wave: 50/(50+50) = 1/2

- No ringing

- No power dissipation in load

- Taps along T-line momentarily see invalid levels

23: I/O

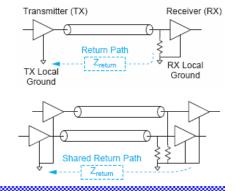

### **Noise and Interference**

- Other sources of intersymbol interference:

- Dispersion

- Caused by nonzero line resistance

- Crosstalk

- Capacitive or inductive coupling between channels

- Ground Bounce

- Nonzero return path impedance

- Simultaneous Switching Noise

23: I/O

### **High-Speed I/O**

- Transmit data faster than the flight time along the line

- Transmitters must generate very short pulses

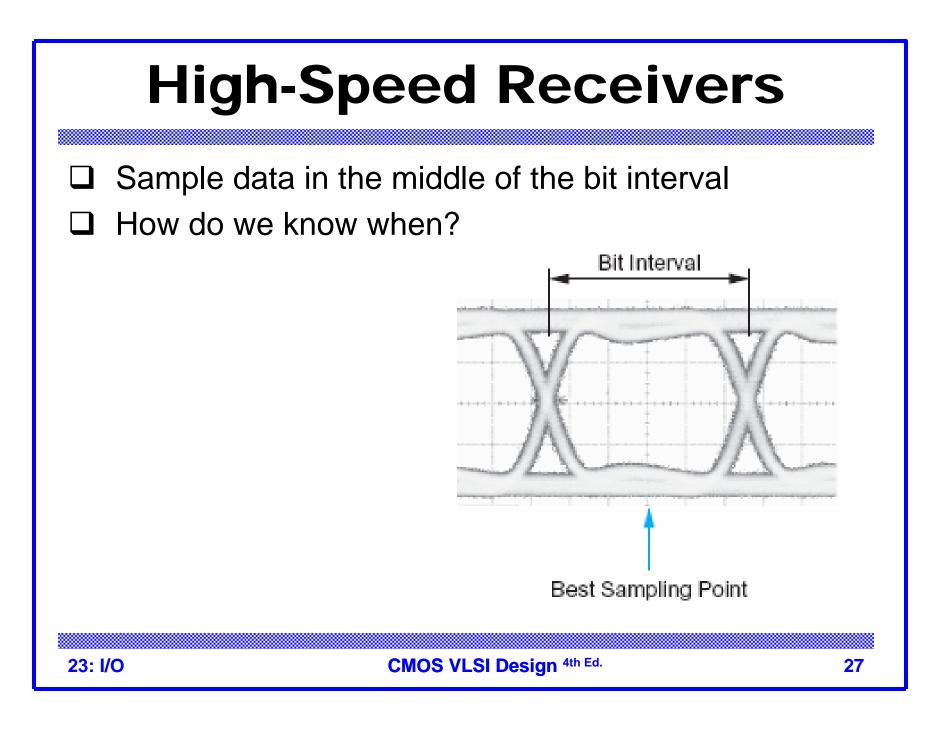

- Receivers must be accurately synchronized to detect the pulses

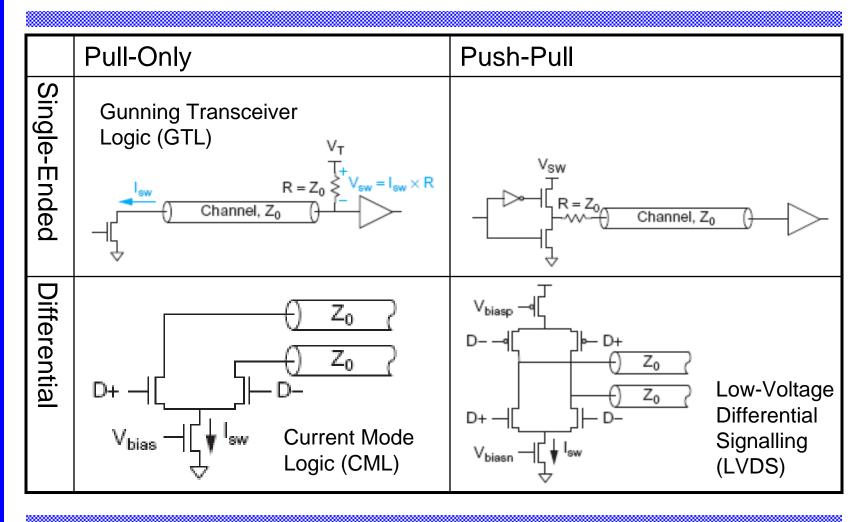

### **High Speed Transmitters**

### □ How to handle termination?

- High impedance current-mode driver + load term?

- Or low-impedance driver + source termination

- □ Single-ended vs. differential

- Single-ended uses half the wires

- Differential is Immune to common mode noise

- **D** Pull-only vs. Push-Pull

- Pull-only has half the transistors

- Push-pull uses less power for the same swing

### **High-Speed Transmitters**

23: I/O

#### CMOS VLSI Design <sup>4th Ed.</sup>

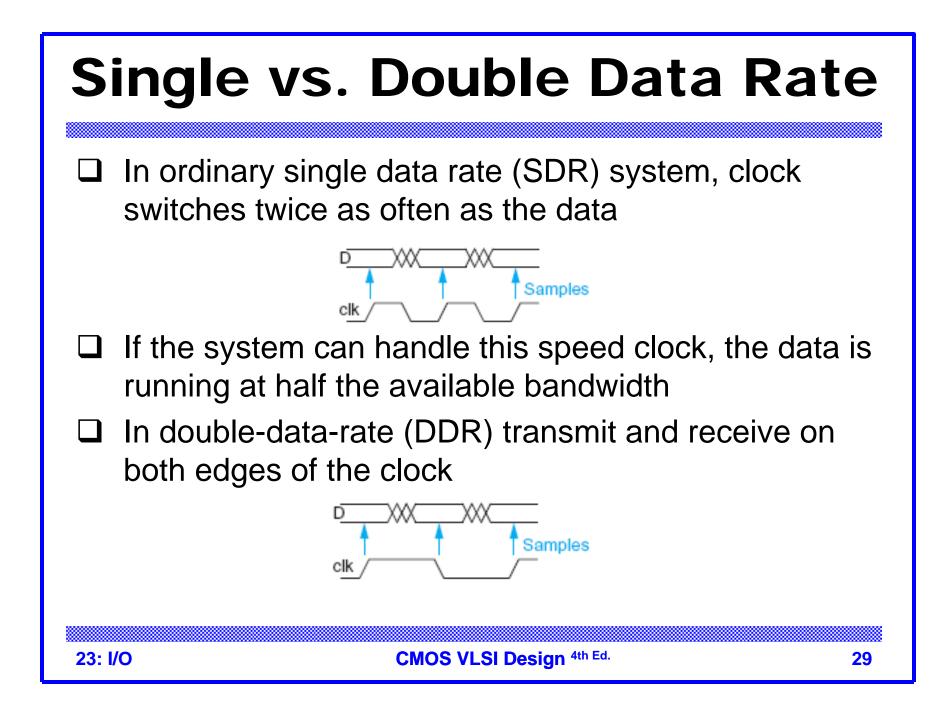

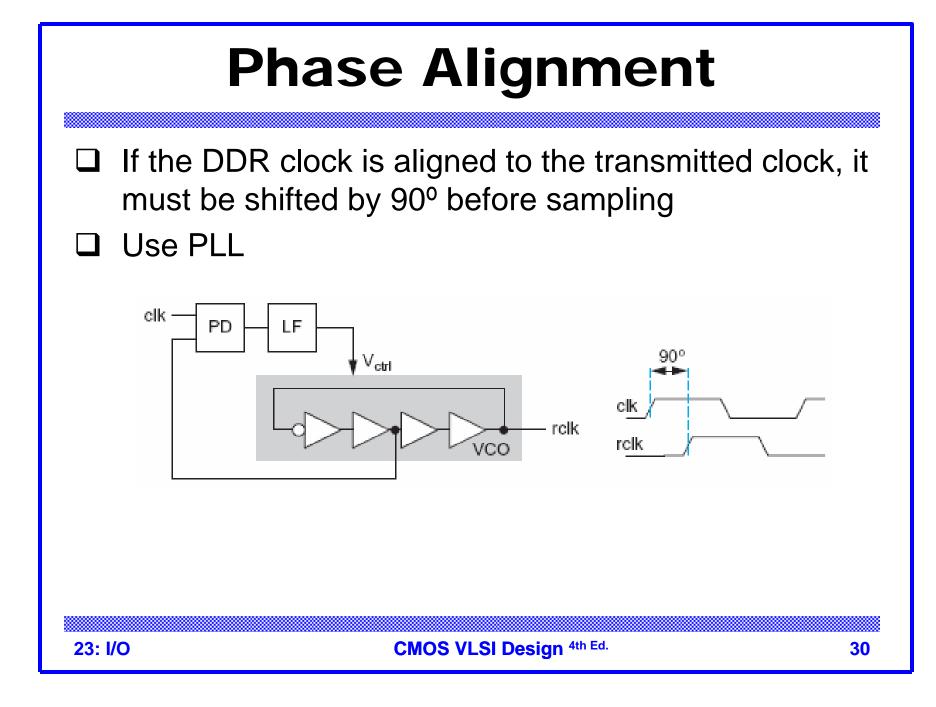

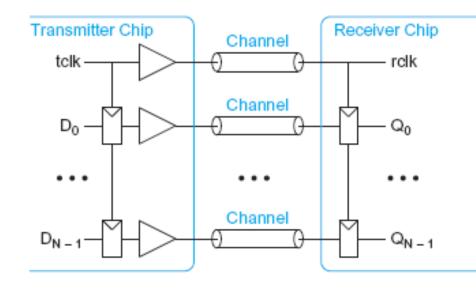

### **Source-Synchronous Clocking**

- □ Send clock with the data

- Flight times roughly match each other

- Transmit on falling edge of tclk

- Receive on rising edge of rclk

23: I/O