# Lecture 22: PLLs and DLLs

### Outline

- □ Clock System Architecture

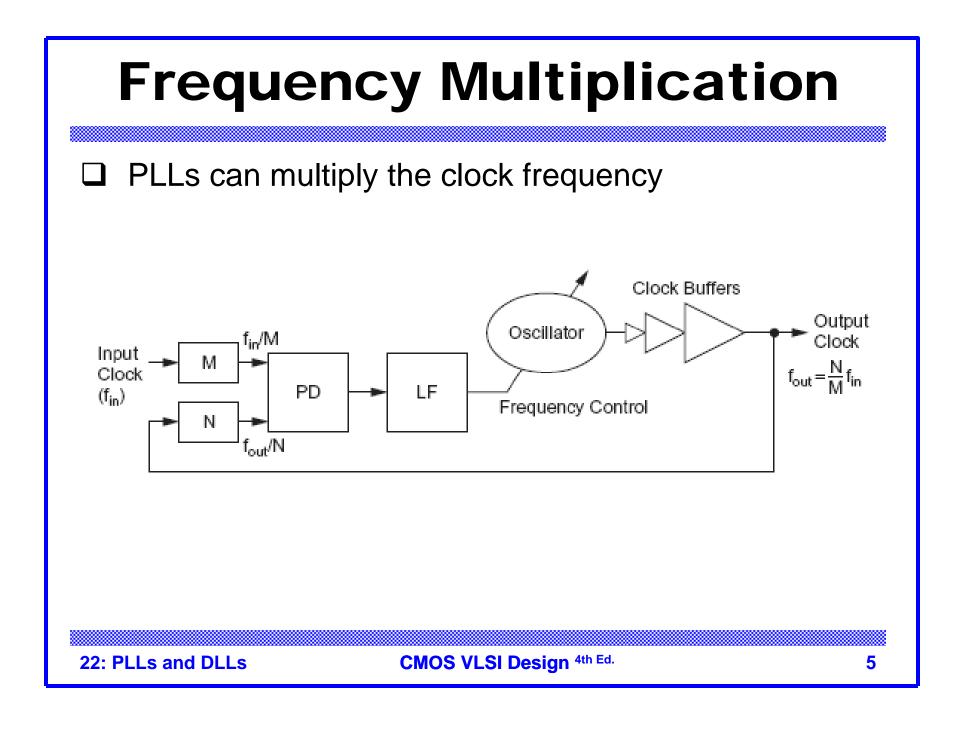

- Phase-Locked Loops

- Delay-Locked Loops

22: PLLs and DLLs

CMOS VLSI Design <sup>4th Ed.</sup>

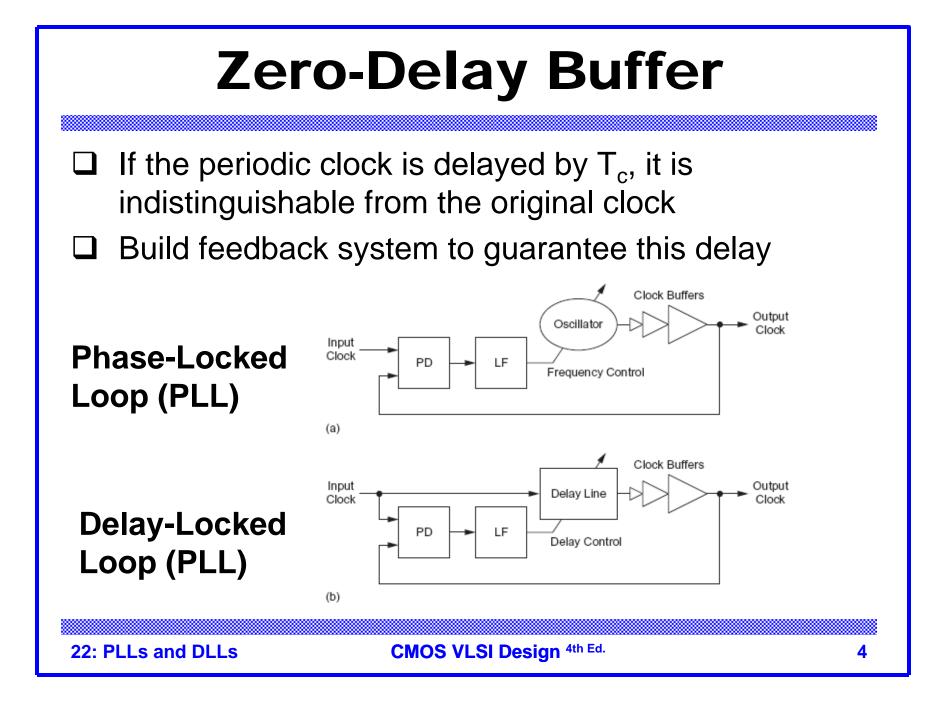

#### **Clock Generation**

□ Low frequency:

- Buffer input clock and drive to all registers

- High frequency

- Buffer delay introduces large skew relative to input clocks

- Makes it difficult to sample input data

- Distributing a very fast clock on a PCB is hard

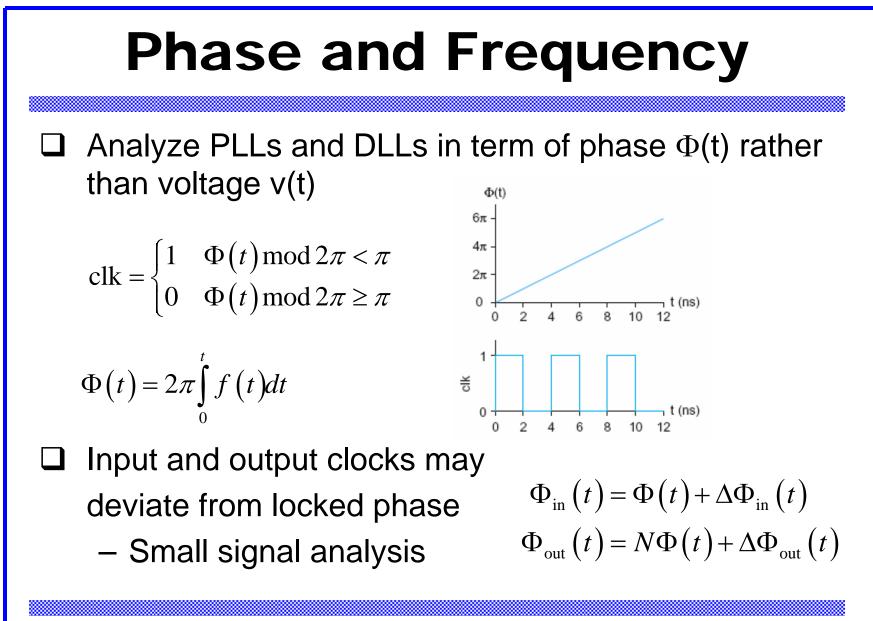

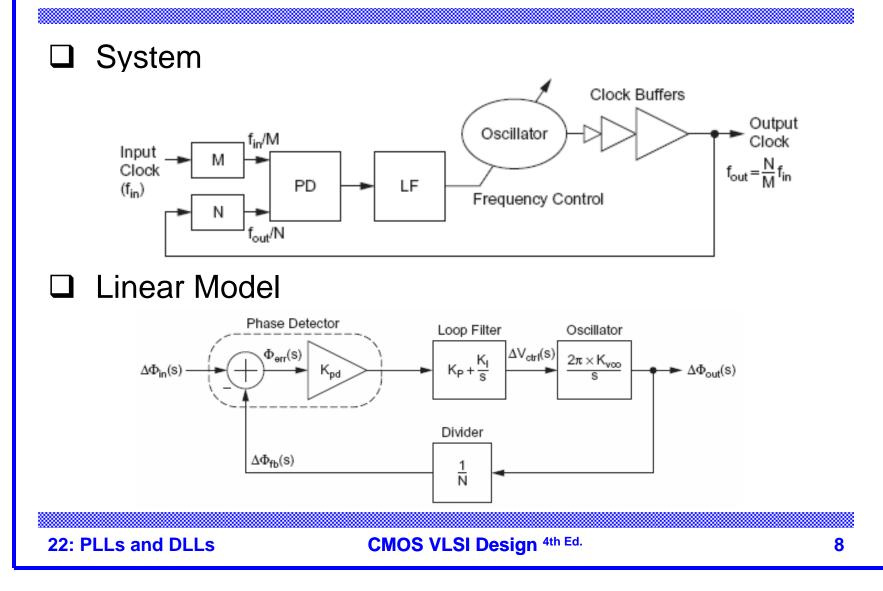

## Linear System Model

- Treat PLL/DLL as a linear system

- Compute deviation DF from locked position

- Assume small deviations from locked

- Treat system as linear for these small changes

- Analysis is not valid far from lock

- e.g. during acquisition at startup

- Continuous time assumption

- PLL/DLL is really a discrete time system

- Updates once per cycle

- If the bandwidth << 1/10 clock freq, treat as continuous</li>

- Use Laplace transforms and standard analysis of linear continuous-time feedback control systems

# Phase-Locked Loop (PLL)

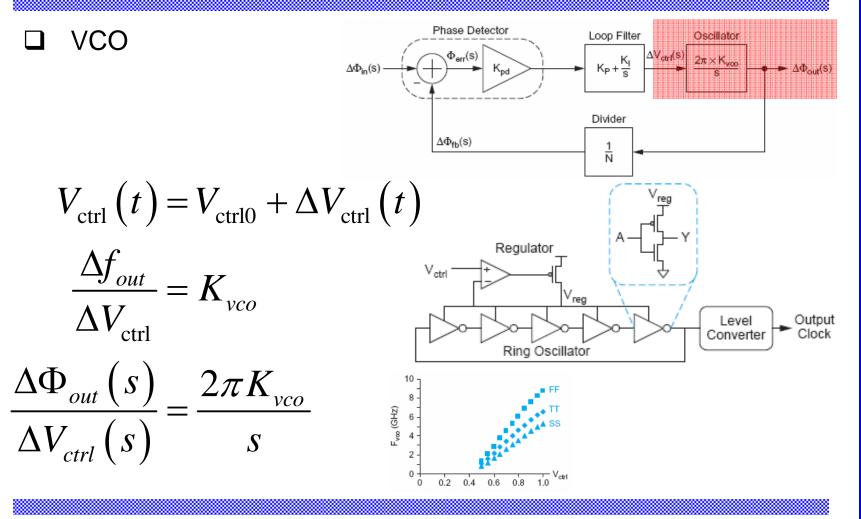

## **Voltage-Controlled Oscillator**

22: PLLs and DLLs

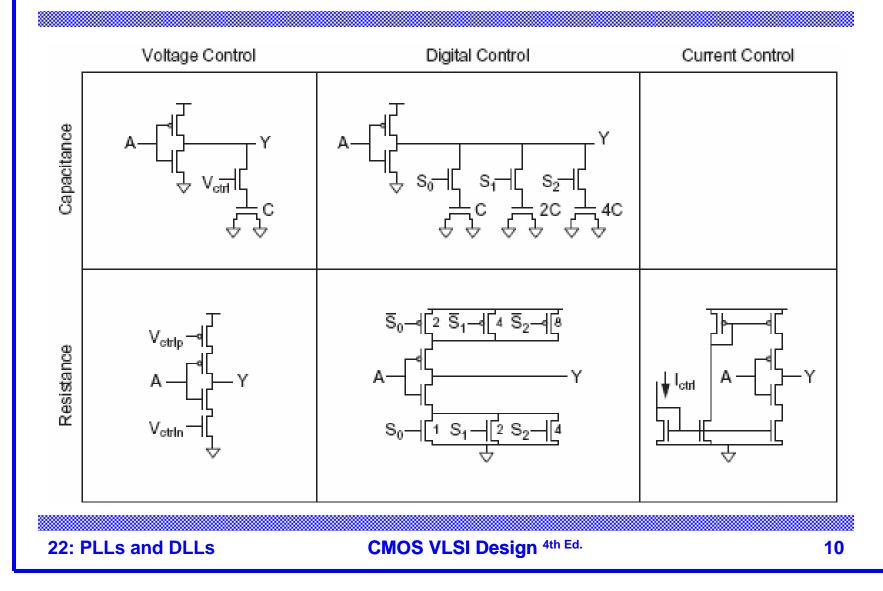

#### **Alternative Delay Elements**

## **PLL Loop Dynamics**

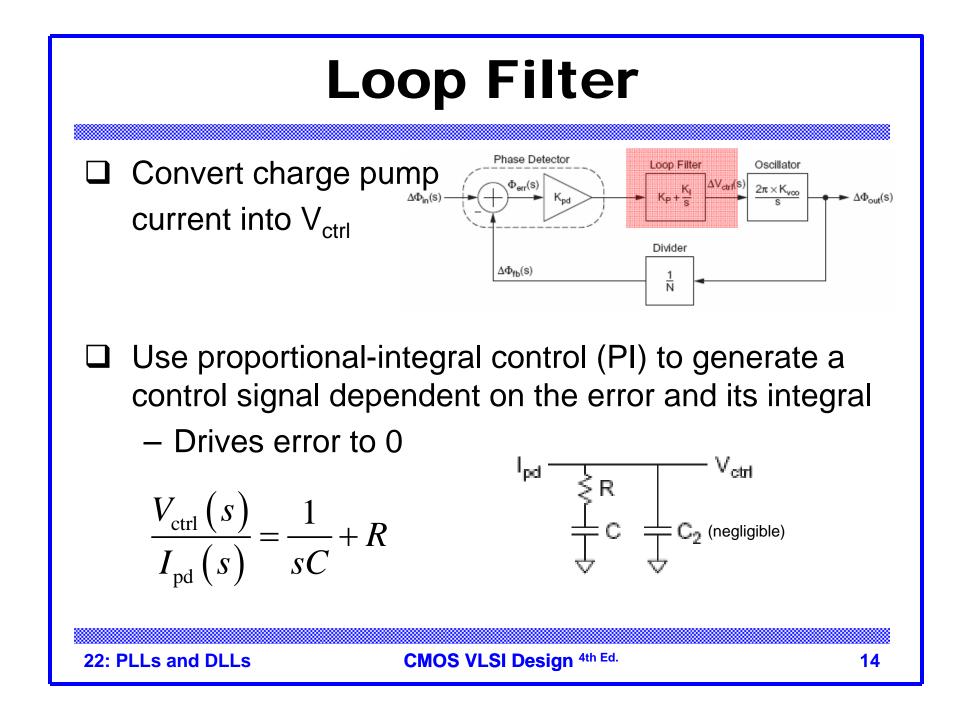

□ Closed loop transfer function of PLL

$$H(s) = \frac{\Delta \Phi_{\text{out}}(s)}{\Delta \Phi_{\text{in}}(s)} = \frac{K_{pd}\left(R + \frac{1}{sC}\right)\frac{2\pi K_{\text{vco}}}{s}}{1 + \frac{1}{N}K_{pd}\left(R + \frac{1}{sC}\right)\frac{2\pi K_{\text{vco}}}{s}}{s}$$

□ This is a second order system

$$H(s) = N \frac{2\zeta\omega_n s + \omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2} \qquad \omega_n = \sqrt{\frac{I_{cp}K_{vco}}{NC}}$$

$$\zeta = \frac{\omega_n}{2}RC$$

$\square \omega_n$  indicates loop bandwidth

22: PLLs and DLLs

$\Box$   $\zeta$  indicates damping; choose 0.7 – 1 to avoid ringing

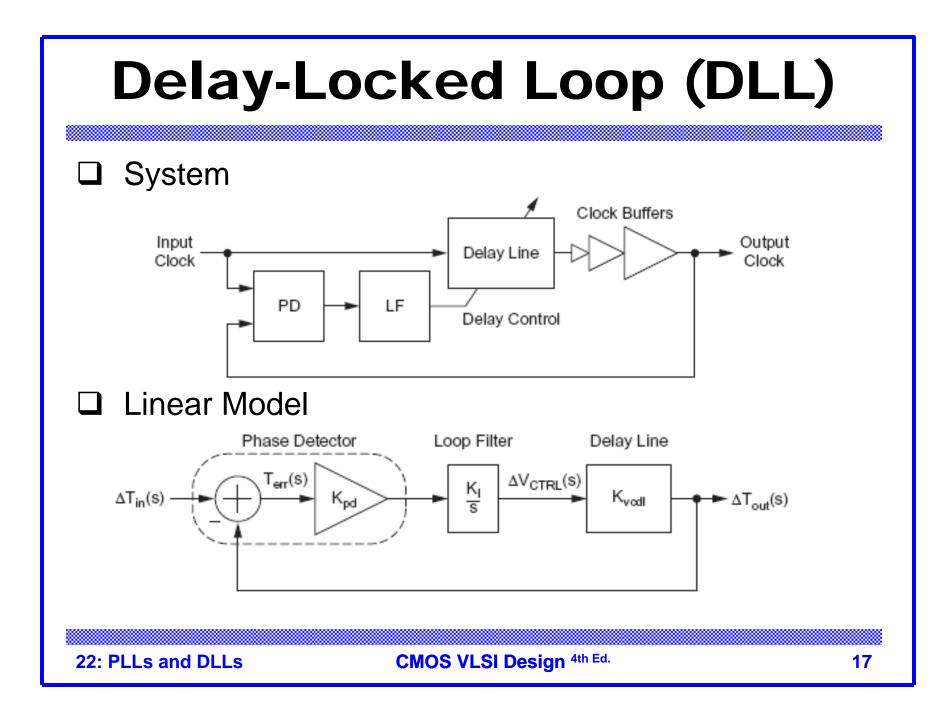

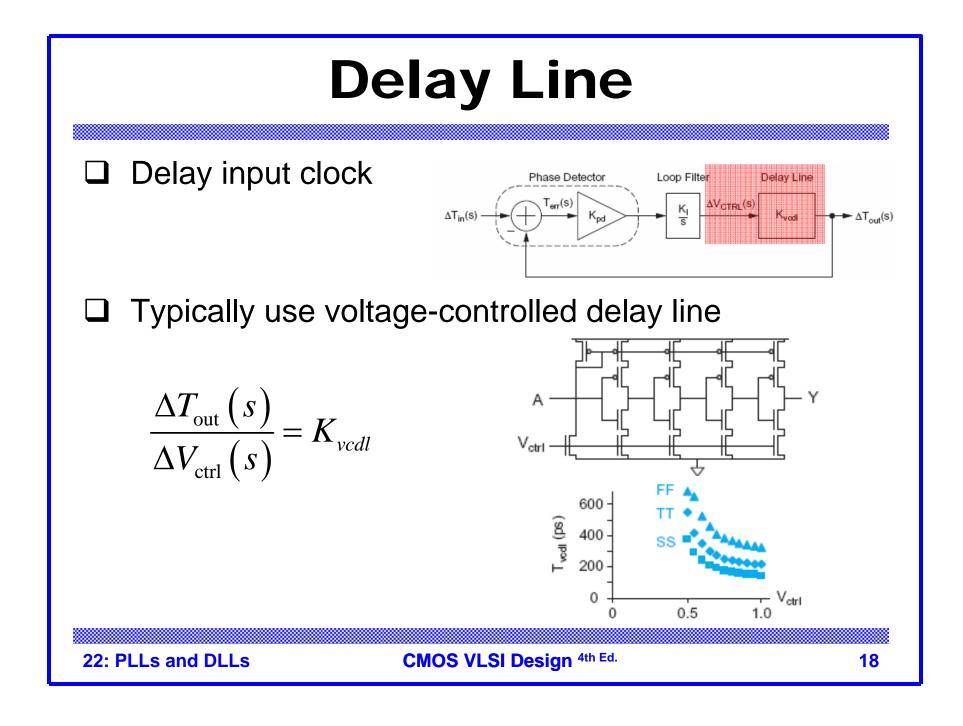

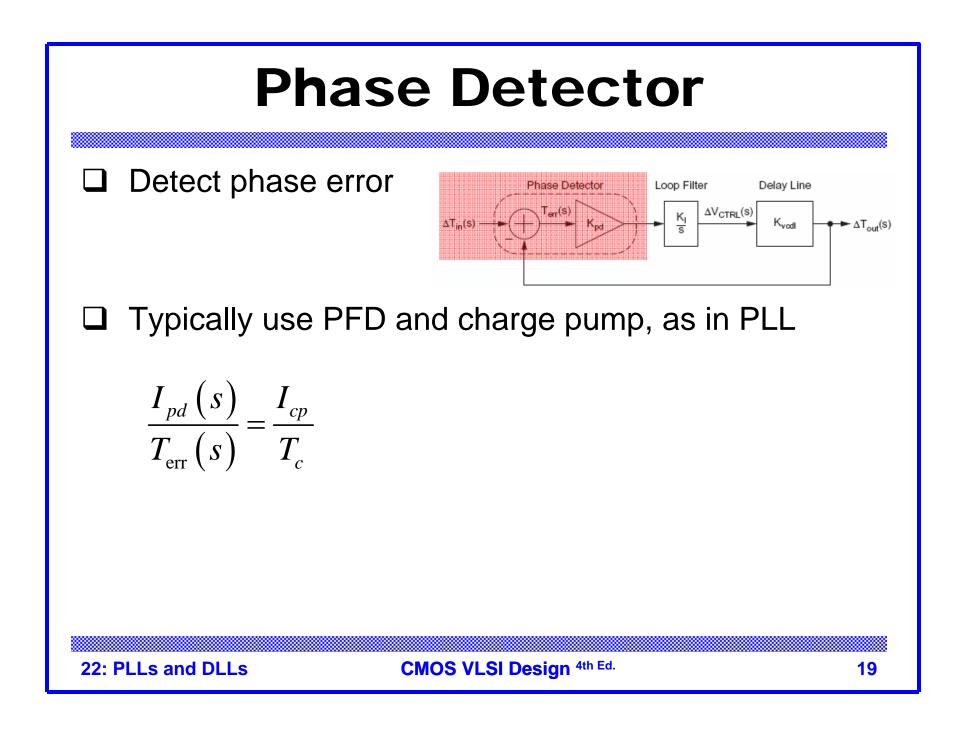

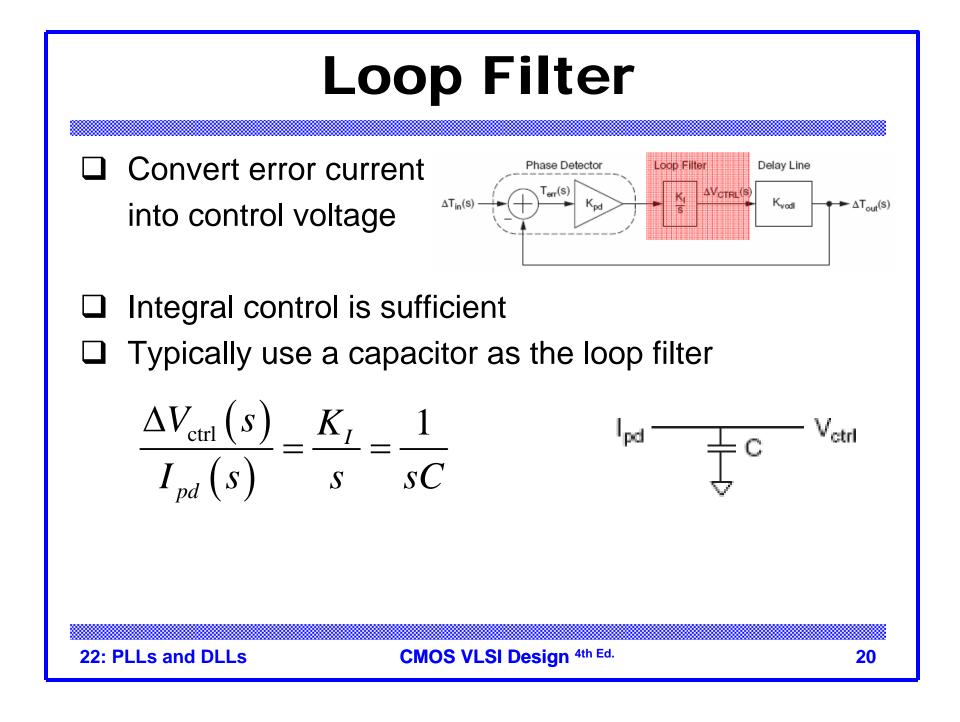

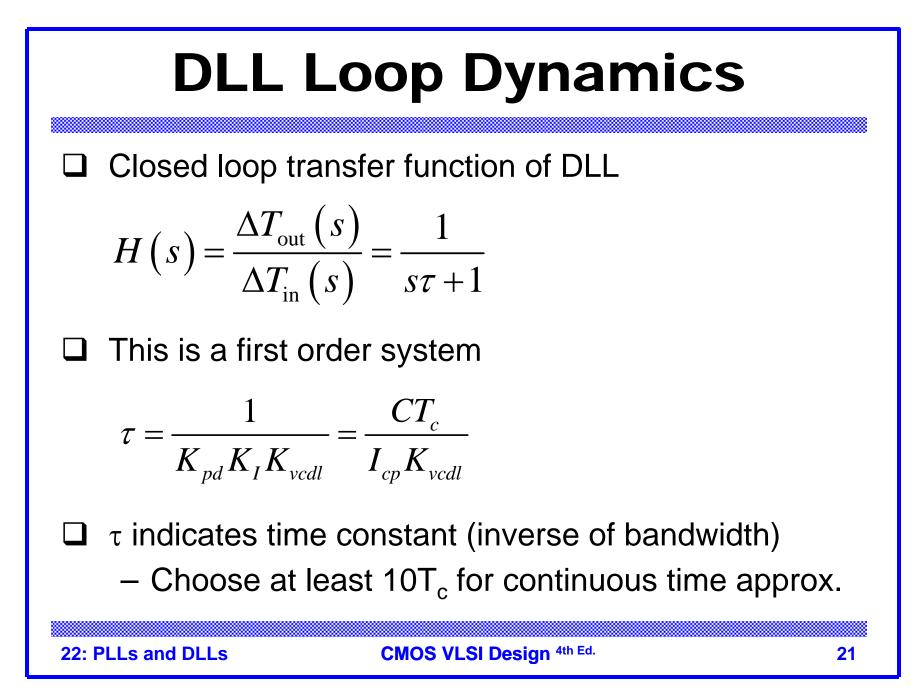

### **Delay Locked Loop**

- Delays input clock rather than creating a new clock with an oscillator

- Cannot perform frequency multiplication

- More stable and easier to design

- 1<sup>st</sup> order rather than 2<sup>nd</sup>

- □ State variable is now time (T)

- Locks when loop delay is exactly  $T_c$

- Deviations of  $\Delta T$  from locked value