## 12T SRAM Cell Basic building block: SRAM Cell Holds one bit of information, like a latch Must be read and written 12-transistor (12T) SRAM cell Use a simple latch connected to bitline 46 x 75 λ unit cell write bit write bit line CMOS VLSI Design 4th Ed. 5

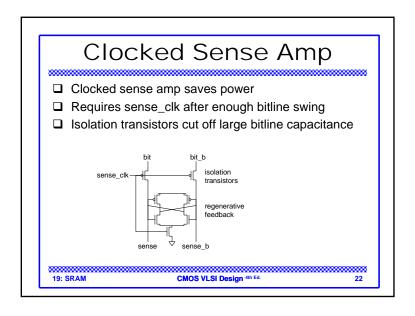

## Differential Pair Amp Differential pair requires no clock But always dissipates static power Sense\_b P1 P2 sense bit N1 N2 bit\_b N3 19: SRAM CMOS VLSI Design 4th Ed. 21

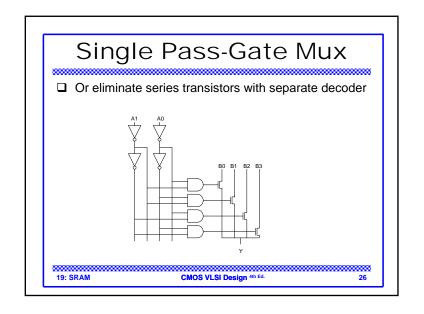

## Tree Decoder Mux ☐ Column mux can use pass transistors ☐ Use nMOS only, precharge outputs ☐ One design is to use k series transistors for 2k:1 mux ☐ No external decoder logic needed