# **Microprocessor-Based Systems (E155)**

Harris

Fall 2004

Lab 3: Multiplexed Display

Due: Week of Sept 27

# Requirement

Display two independent hexadecimal numbers on your dual seven-segment display. Use your DIP switch and four wires to provide the data for two hexadecimal numbers. You must use a single seven segment decoder module to drive the cathodes for both digits on the display, which therefore must be wired for multiplexed operation. Also, display the sum of the numbers on five LEDs on your utility board.

### **Suggested Approach**

- Understand what a multiplexed display is, and how it can be implemented.

- Learn how transistors can be used to control the switching of the dual seven-segment display.

- Determine how to generate the timing signals required for multiplexing the display.

- Write a Verilog module performing the multiplexing and summation.

- Implement and debug your circuit.

# Discussion

### **Multiplexed Display**

Multiplexing is a technique that is widely used to reduce wiring complexity. It can be used to reduce the number of wires that must be run from one point to another in a system, or as in this case, to reduce the number of pins on a package (the display package, here).

A "multiplexed" common anode display is one in which the anode of all the segments in a given digit are connected to a common point, and the cathode of each

#### LABORATORY #3: Multiplexed Display

segment of one digit is connected to the cathode of the corresponding segment of the other digit. The output signals from the display driver are connected to the shared cathode connections. These shared cathodes are then "time shared" by the left and right digits (i.e., the display data is *time multiplexed*). Data for the numeral that is to appear on the right digit is applied to the cathodes while the right shared (or *common*) anode is pulled high, and data for the left numeral is applied to the cathodes while the left anode is pulled high. By rapidly alternating the applied data for the two desired numerals while alternately (and synchronously) pulling high the two common anode contacts, the eye will perceive the two separate numerals as being continuously lit, with no perceptible flicker.

#### Using a Transistor as a Switch

How can we alternately pull high the left digit and right digit anodes? Remember that each LED draws about 15 mA at full brightness, so a complete 7-segment display needs about 100 mA from the anode. If you drove the anode directly with an FPGA output, you would find the FPGA only supplies a few mA of current and so the LEDs would be very dim. We need some type of device that will act as a switch, either behaving as an open circuit or as nearly a short circuit, that we can control with an electrical signal. A bipolar junction transistor (BJT) can serve this function.

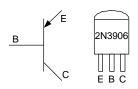

A PNP transistor behaves as a reasonably good switch for pulling signals high. The PNP transistor has 3 terminals: the emitter, base, and collector. When the emitter is tied to VDD and the base is also driven high, we can say that "looking into" the collector, we see an open circuit. When the base is driven low, we see a high conductance path from the collector to VDD.

Unfortunately, a small amount of current also flows into the base of the PNP transistor. If we drive the base low without limiting this current, the transistor may be damaged. Therefore, place a resistor in series with the circuit driving the base to prevent more than about 2 mA of current from flowing.

A popular PNP transistor for low-power applications is the 2N3906. Looking at the flat labeled side, the pins, from left to right, are the emitter, base, and collector. Use the proper symbol when drawing your schematics.

# Verilog Hints

- This lab has no tools tutorial. You're much more on your own. Consult the on-line help and ask your friends when you get stuck. Learning to operate new and buggy tools is a major part of the work of most practicing chip designers.

- Be sure your design requires only one decoder even though you are driving two multiplexed displays.

- Our Verilog tools do not like having signals and modules with the same name.

# **Construction hints**

- Don't forget the current-limiting resistors when connecting your 7-segment display and in series with the base of the transistors.

- Use the four DIP switches to provide one set of inputs. Connect wires from four other pins of your FPGA board to  $V_{DD}$  or GND to provide the other four inputs. Or use an extra set of DIP switches with the appropriate pullup resistors.

- Don't forget to show the sum of the numbers on 5 LEDs.

- You will probably find that at 1 or 2 MHz, the 7-segment displays are toggling so fast that data from one blurs onto the other. You can solve this problem by constructing a circuit to reduce the frequency of the signal multiplexing the displays.

- If you leave your reset input floating, strange and wonderful things will happen to your resettable flops! You should understand why.

# What to Turn In

When you are done, have your lab checked off by the instructor. You should thoroughly understand how it works and what would happen if any changes were made. Turn in your lab notebook including the following information:

- Your design approach

- Schematics of the breadboarded circuit

- Your Verilog code and simulation results

- For each module: schematics of the synthesis results, an report of how many CLBs are produced, why that many are needed, and whether this is a minimal number

- How many hours did you spend on the lab? This will not count toward your grade.